- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362444 > AS5SS256K18DB-8 x18 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | AS5SS256K18DB-8 |

| 英文描述: | x18 Fast Synchronous SRAM |

| 中文描述: | x18快速同步SRAM |

| 文件頁(yè)數(shù): | 14/16頁(yè) |

| 文件大小: | 224K |

| 代理商: | AS5SS256K18DB-8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)

SRAM

AS5SS128K36

Austin Semiconductor, Inc.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

14

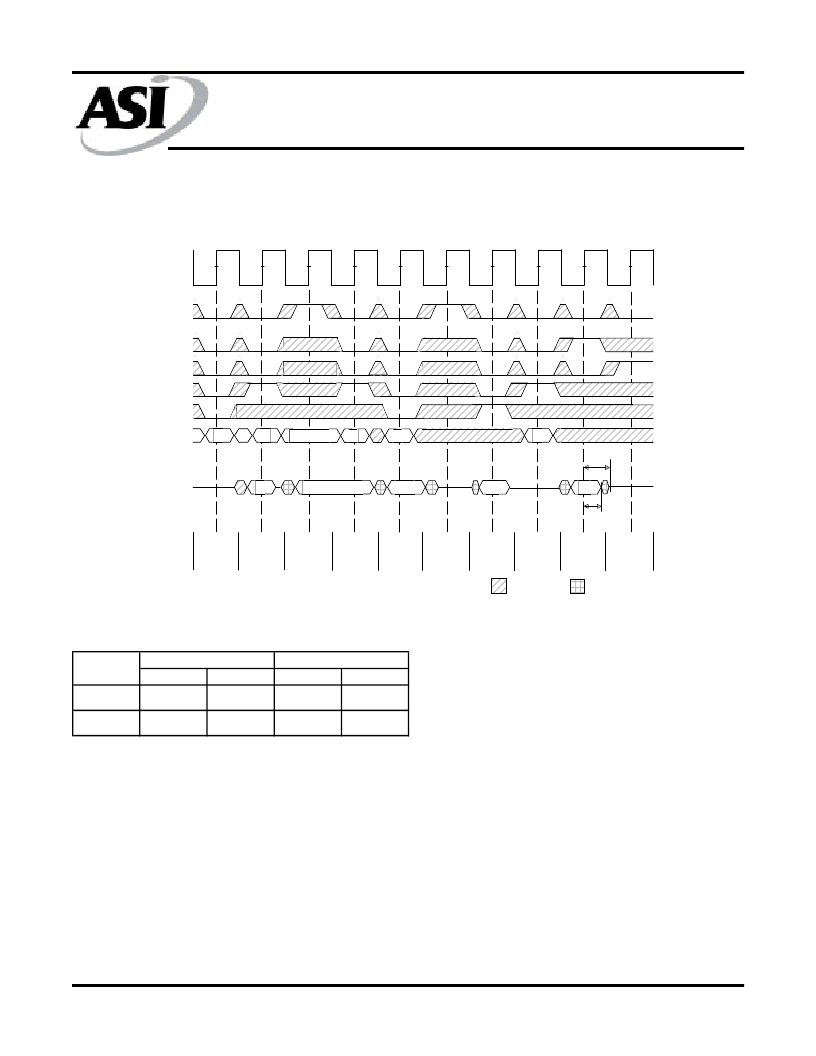

NOP, STALL AND DESELECT CYCLES

123

123

123

123

1234

1234

1234

1234

1234

1234

1234

1234

A1

1234

1234

1234

1234

1234

1234

12345678901234567890123

12345678901234567890123

12345678901234567890123

123

123

123

1234567890123456

1234567890123456

1234567890123456

1234

1234567890123456789012

1234567890123456789012

1234567890123456789012

A2

12

12

12

12

12

12

A3

123

123

123

A4

112345678901234

112345678901234

112345678901234

A5

112345678901234

112345678901234

112345678901234

t

KHQZ

123

123

123

D(A1)

1234

1234

1234

1234

Q(A2)

123

123

123

123

Q(A3)

123

123

123

123

Q(A5)

12

12

12

12

WRITE

D(A1)

READ

Q(A2)

STALL

READ

Q(A3)

WRITE

D(A4)

STALL

NOP

READ

Q(A5)

DESELECT CONTINUE

DESELECT

123

123

123

Don’t Care

1234

1234

1234

1234

Undefined

CLK

CE\

ADV/LD\

R/W\

BWx\

ADDRESS

DQ

COMMAND

1

2 3 4 5 6 7 8 9 10

t

KHQX

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

123

123

123

123

1234

1234

1234

1234

123

123

123

123

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

CKE\

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

1234

12345678

12345678

12345678

12

12

12

12

12

123

123

123

123

123

123

123

1234

1234

1234

1234

1234

1234

1234

12345678

12345678

12345678

12345678

12345678

12345678

12

12

12

12

12

12

12

12

12

12

12

12

1234567890

1234567890

1234567890

123456789

123456789

123456789

123456789

123456789

123456789

12

12

12

12

12

12

1234

1234

1234

123456789

123456789

12345678

12345678

12345678

12

12

12

12

12

12

12

12

12

12

D(A4)

NOP, STALL AND DESELECT TIMING PARAMETERS

-11

MIN

3.0

MAX

MIN

3.0

MAX

t

KHQX

t

KHQZ

5.0

5.0

SYMBOL

-12

NOTE:

1.

The IGNORE CLOCK EDGE or STALL cycle (clock 3) illustrates CKE\ being used to create a “pause”. A WRITE is not performed

during this cycle.

For this waveform, ZZ and OE\ are tied LOW.

CE\ represents three signals. When CE\ = 0, it represents CE\ = 0, CE2\ = 0, CE2 = 1.

Data coherency is provided for all possible operations. If a READ is initiated, the most current data is used. The most recent data

may be from the input data register.

2.

3.

4.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5SS256K18DB-9 | x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-10 | x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-8 | x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-9 | x18 Fast Synchronous SRAM |

| AS5SS256K36 | 9216Kbits 256K x 36 Replacement with DSCC 5962-n/a | SSRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS5SS256K18DB-9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-10/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-10/XT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。