- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362444 > AS5SS256K18DB-9 x18 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號: | AS5SS256K18DB-9 |

| 英文描述: | x18 Fast Synchronous SRAM |

| 中文描述: | x18快速同步SRAM |

| 文件頁數(shù): | 2/16頁 |

| 文件大小: | 224K |

| 代理商: | AS5SS256K18DB-9 |

SRAM

AS5SS128K36

Austin Semiconductor, Inc.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

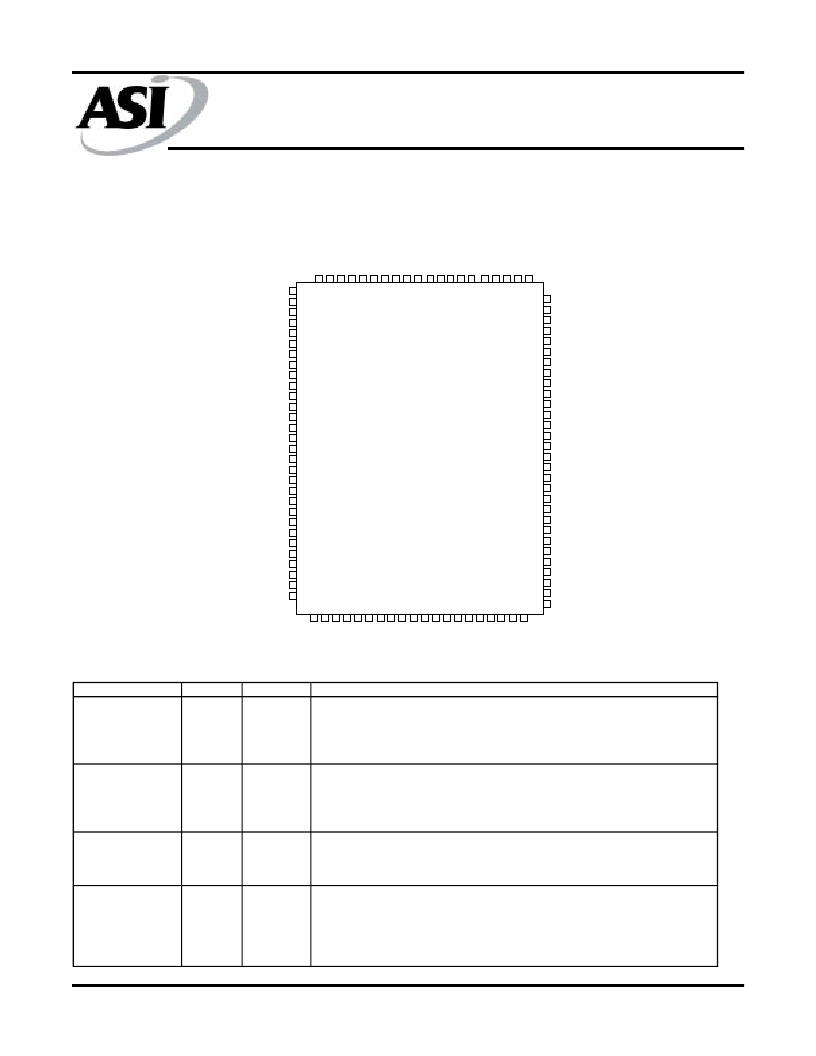

PIN ASSIGNMENT

(Top View)

100-pin TQFP (DQ)

PIN DESCRIPTIONS

TQFP PINS

37

36

32-35, 44-50,

81, 82, 99, 100

SYMBOL

SA0

SA1

SA

TYPE

Input

DESCRIPTION

Synchronous Address Inputs: These inputs are registered and must meet the setup

and hold times around the rising edge of CLK. Pins 83 and 84 are reserved as

address bits for the higher-density 8Mb and 16Mb ZBL SRAMs, respectively. SA0 and

SA1 are the two least significant bits (LSB) of the address field and set the internal

burst counter if burst is desired.

Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to

be written when a WRITE cycle is active and must meet the setup and hold times

around the rising edge of CLK. BYTE WRITEs need to be asserted on the same cycle

as the address. BWa\ controls DQa pins; BWb\ controls DQb pins; BWc\ controls

DQc pins; BWd\ controls DQd pins.

Synchronous Clock Enable:

This active LOW input permits CLK to propagate

throughout the device. When CKE is HIGH, the device ignores the CLK input and

effectively internally extends the previous CLK cycle. This input must meet setup and

hold times around the rising edge of CLK.

Read/Write: This input determines the cycle type when ADV/LD\ is LOW and is the

only means for determining READs and WRITEs. READ cycles may not be converted

into WRITEs (and vice versa) other than by loading a new address. A LOW on this pin

permits BYTE WRITE operations and must meet the setup and hold times around the

rising edge of CLK. Full bus-width WRITEs occur if all byte write enables are LOW.

93

94

95

96

BWa\

BWb\

BWc\

BWd\

Input

87

CKE\

Input

88

R/W\

Input

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

DQc

DQc

DQc

V

DD

Q

V

SS

DQc

DQc

DQc

DQc

V

SS

V

Q

DQc

DQc

V

SS

V

DD

V

DD

V

SS

DQd

DQd

V

DD

Q

V

SS

DQd

DQd

DQd

DQd

V

SS

V

Q

DQd

DQd

DQd

DQb

DQb

DQb

V

DD

Q

V

DQb

DQb

DQb

DQb

V

SS

V

Q

DQb

DQb

V

SS

V

SS

V

DD

ZZ

DQa

DQa

V

DD

Q

V

DQa

DQa

DQa

DQa

V

SS

V

Q

DQa

DQa

DQa

M

S

S

S

S

S

S

D

D

S

V

D

D

D

S

S

S

S

S

S

S

S

S

C

C

B

B

B

B

C

V

D

V

S

C

R

C

O

A

N

N

S

S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5SS256K18DQ-10 | x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-8 | x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-9 | x18 Fast Synchronous SRAM |

| AS5SS256K36 | 9216Kbits 256K x 36 Replacement with DSCC 5962-n/a | SSRAM |

| AS5SS256K36A | 256K x 36 SSRAM Flow-Through. Synchronous Burst SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS5SS256K18DQ-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-10/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-10/XT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-8/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。