- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄166232 > AS5SS256K18DQ-10/IT (AUSTIN SEMICONDUCTOR INC) 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through PDF資料下載

參數(shù)資料

| 型號(hào): | AS5SS256K18DQ-10/IT |

| 廠商: | AUSTIN SEMICONDUCTOR INC |

| 元件分類: | SRAM |

| 英文描述: | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| 中文描述: | 256K X 18 STANDARD SRAM, 10 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 2/13頁(yè) |

| 文件大小: | 135K |

| 代理商: | AS5SS256K18DQ-10/IT |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)

AS5SS256K18

Rev. 2.1 06/05

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

10

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

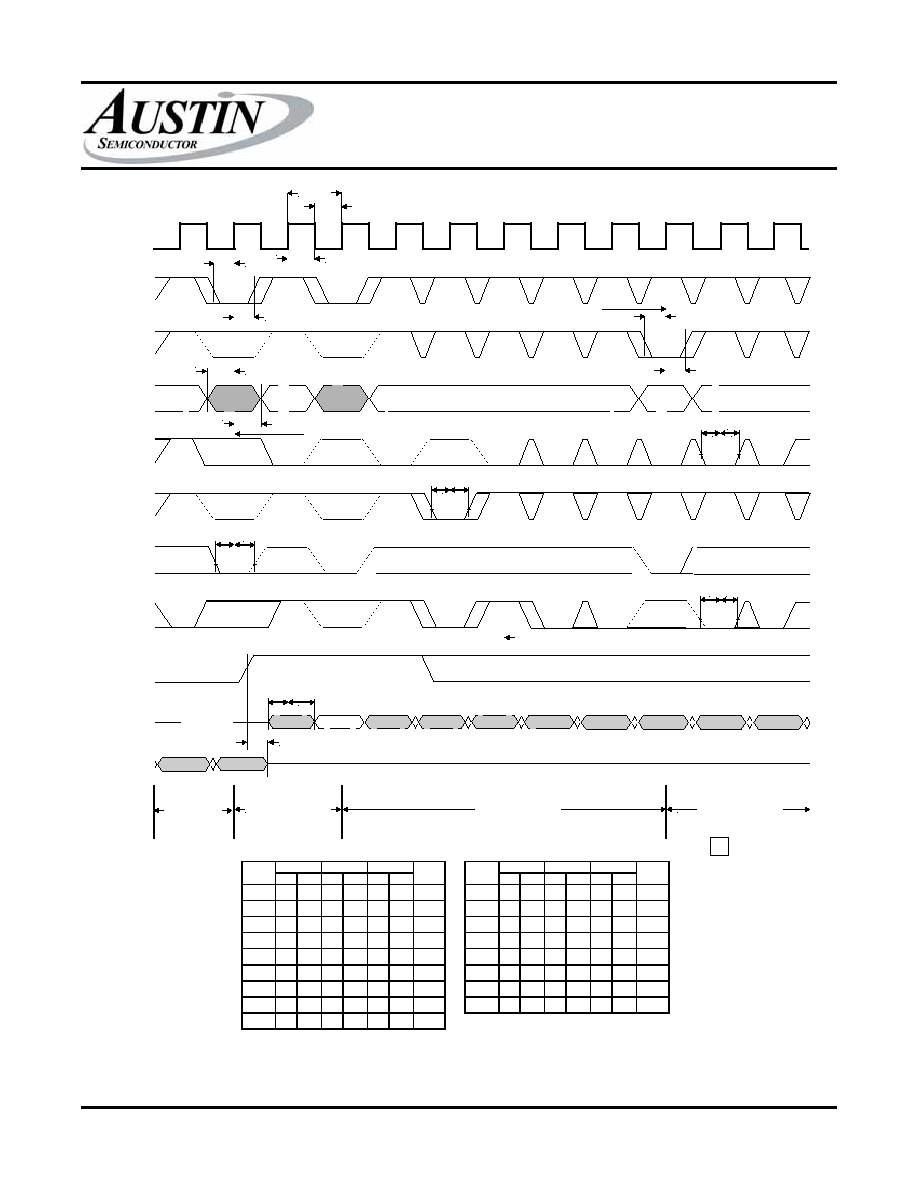

NOTE: 1. D(A2) refers to output from address A2. D(A2+1) refres to output from the next internal burst address following A2.

2. CE2\ and CE2 have timing identical to CE\. On this diagram, when CE\ is LOW, CE2\ is LOW and CE2 is HIGH. When CE\ is HIGH, CE2\ is HIGH and CE2 is LOW.

3. OE\ must be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents input/output data contention for the time period

prior to the byte write enable inputs being sampled.

4. ADV\ must be HIGH to permit a WRITE to the loaded address.

5. Full-width WRITE can be initiated by GW\ LOW; or GW\ HIGH and BWE\, BWa\ and BWb\ LOW.

WRITE TIMING

MIN MAX MIN MAX MIN MAX

tKC

8.8

10

15

ns

tDS

1.5

1.8

2.0

ns

tKF

113

100

66

MHz

tCES

1.5

1.8

2.0

ns

tKH

2.5

3.0

4.0

ns

tAH

0.5

ns

tKL

2.5

3.0

4.0

ns

tADSH

0.5

ns

tOEHZ

4.2

5.0

ns

tAAH

0.5

ns

tAS

1.5

1.8

2.0

ns

tWH

0.5

ns

tADSS

1.5

1.8

2.0

ns

tDH

0.5

ns

tAAS

1.5

1.8

2.0

ns

tCEH

0.5

ns

tWS

1.5

1.8

2.0

ns

-10

-9

-8

SYM

-10

UNITS

SYM

-8

-9

WRITE TIMING PARAMETERS

1234

123456789

1234

12345

123456

1234

1234567890

12345

1234

1234567890

12345

1234

123456789012

123456

12

12345

123456789

12345

1234

1234567890

12345

123456789

12345

1234

123456789

12345

1234

1234567890

12345

123456789

12345

CLK

ADSP\

ADSC\

○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○

○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○

○

○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○

○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○

○

○○○○○○○○○○○○○○○○○○○○○○

○○○○○○

○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○

○○○○○○○○○○○○○○○○○

ADDRESS

A2

BEW\,

BWa\ - BWb\

○○○○○○○○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

CE\

(NOTE 2)

ADV\

OE\

SINGLE WRITE

BURST WRITE

GW\

○

○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○○

D

Extended

BURST WRITE

1234

A1

12345678

123

12345678

1234567890123456789012345678901212345678901234

12

1

A3

12345678

123456789012345678901

12

123456789012345678

1234567890123456789012345678901212345678901234567890123456789012123456789012

D(A2)

D(A2+2)

12

D(A2+3)

12

D(A3)

12

D(A3+1)

12

D(A3+2)

123456

1234

123456

1234567

123456

12345678

1234567

12

1234

123456

1234

1234567890123456789012345678901212345678901234567890

12345

1234567

1234567890123456789012345

12

12345

123456

D(A1)

D(A2+1)

t

ADSS

t

ADSH

t

KC

t

KL

t

KH

t

AS

t

AH

123456

t

ADSS

t

ADSH

123456

ADSC\ extends burst.

BYTE WRITE signals are ignored

when ADSP\ is LOW.

t

WS

t

WH

t

WS

t

WH

(Note 5)

123456

123456789

1234567

123456789

12345

t

CES

t

CEH

t

AAS tAAH

(Note 4)

ADV\ suspends burst.

(Note 3)

Q

1234

12345

123456

12

t

OEHZ

12

D(A2+1)

123

12

(Note 1)

High-Z

BURST

READ

12345

Don’t Care

t

DS

t

DH

12345678901234567

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5SS256K18DQ-10/XT | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-9/IT | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-9/XT | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-8IT | 256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K36ADQ-8.5/883C | 256K x 36 SSRAM Flow-Through, Synchronous Burst SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS5SS256K18DQ-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-8/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-8IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

| AS5SS256K18DQ-9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Fast Synchronous SRAM |

| AS5SS256K18DQ-9/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K x 18 SSRAM Synchronous Burst SRAM, Flow-Through |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。