- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379689 > ASC7512D8 (Electronic Theatre Controls, Inc.) DIGITAL TEMPERATURE SENSOR WITH INTEGRATED FAN CONTROL PDF資料下載

參數(shù)資料

| 型號: | ASC7512D8 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 溫度/濕度傳感器 |

| 英文描述: | DIGITAL TEMPERATURE SENSOR WITH INTEGRATED FAN CONTROL |

| 中文描述: | 數(shù)字溫度傳感器整合了風(fēng)扇控制 |

| 文件頁數(shù): | 16/35頁 |

| 文件大?。?/td> | 337K |

| 代理商: | ASC7512D8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

- 16 -

Andigilog, Inc. 2006

www.andigilog.com

August 2006 - 70A05003

aSC7512

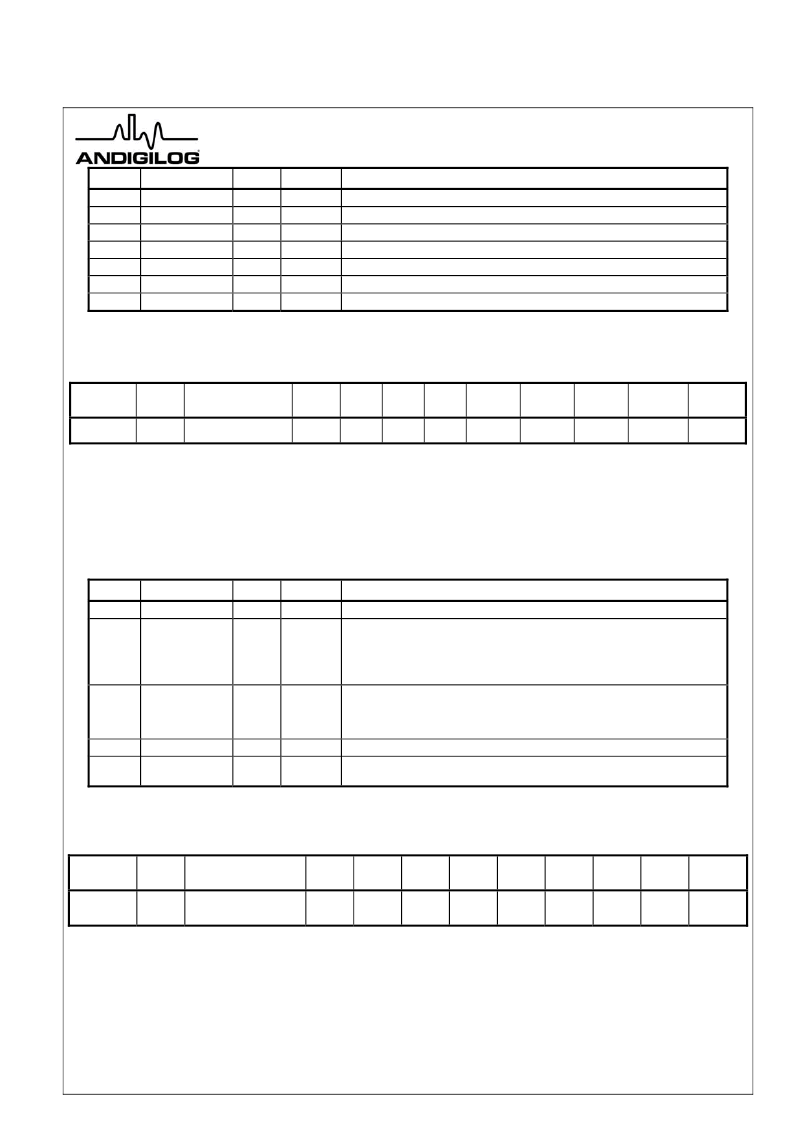

Bit

Name

R/W

Default

Description

1:0

RESERVED

R

0

RESERVED

2

ROPEN

R

0

ZONE 1 (REMOTE) SENSOR OPEN-CIRCUIT

3

RLOW

R

0

ZONE 1 (REMOTE) SENSOR

≤

LOW LIMIT

4

RHIGH

R

0

ZONE 1 (REMOTE) SENSOR > HIGH LIMIT

5

6

LLOW

LHIGH

R

R

0

0

ZONE 2 (LOCAL) SENSOR

≤

LOW LIMIT

ZONE 2 (LOCAL) SENSOR > HIGH LIMIT

7

BUSY

R

0

CONVERTER IN PROCESS OF CONVERSION

Table 5 Alert Status Register

Register 41h: Interrupt Status Register 1

Register

Address

Read/

Write

Register Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

41h

R

Interrupt Status 1

ERR

RES

ZN2

ZN1

RES

RES

RES

RES

00

The Interrupt Status Register 1 bits will be automatically set, by the aSC7512, whenever a fault condition is detected. A fault

condition is detected whenever a measured value is outside the window set by its limit registers. ZN1 bit will be set when a

diode fault condition, such as an open or short, is detected. More than one fault may be indicated in the interrupt register

when read. The register will hold a set bit(s) until the event is read by software. The contents of this register will be cleared

(set to 0) automatically by the aSC7512 after it is read by software, if the fault condition no longer exists. Once set, the

Interrupt Status Register 1 bits will remain set until a read event occurs, even if the fault condition no longer exists. This

register is read-only – a write to this register has no effect.

Bit

Name

R/W

Default

Description

3:0

RES

R

0

Reserved

4

Zone 1 Limit

Exceeded

R

0

The aSC7512 automatically sets this bit to 1 when the temperature input

measured by the Remote1- and Remote1+ inputs is less than or equal to the

limit set in the Processor (Zone 1) Low Temp register or more than the limit

set in the Processor (Zone 1) High Temp register. This bit will be set when a

diode fault is detected.

5

Zone 2 Limit

Exceeded

R

0

The aSC7512 automatically sets this bit to 1 when the temperature input

measured by the internal temperature sensor is less than or equal to the limit

set in the thermal (Zone2) Low Temp register or greater than the limit set in

the Internal (Zone2) High Temp register.

6

RES

R

0

Reserved

7

Error in Status

Register 2

R

0

If there is a set bit in Status Register 2, this bit will be set to 1.

Table 6 Interrupt Status Register 1

Register 42h: Interrupt Status Register 2

Register

Address

Read/

Write

Register Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

42h

R

Interrupt Status 2

RES

ERR1

RES

RES

RES

FAN

RES

RES

00

The Interrupt Status Register 2 bits will be automatically set, by the aSC7512, whenever a fault condition is detected.

Interrupt Status Register 2 identifies faults caused by temperature sensor error, fan speed dropping below minimum set by

the tachometer minimum register. Interrupt Status Register 2 will hold a set bit until the event is read by software. The

contents of this register will be cleared (set to 0) automatically by the aSC7512 after it is read by software, if fault condition

no longer exists. Once set, the Interrupt Status Register 2 bits will remain set until a read event occurs, even if the fault no

longer exists. This register is read-only – a write to this register has no effect.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASC7512M8 | DIGITAL TEMPERATURE SENSOR WITH INTEGRATED FAN CONTROL |

| ASC7521A | LOW- OLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR |

| ASC7521AM8 | LOW- OLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR |

| ASC7531A | LOW-VOLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR AND VOLTAGE MONITOR |

| ASC7531AM10 | LOW-VOLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR AND VOLTAGE MONITOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ASC7512M8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DIGITAL TEMPERATURE SENSOR WITH INTEGRATED FAN CONTROL |

| ASC7521A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LOW- OLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR |

| ASC7521AM8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LOW- OLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR |

| ASC7531A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LOW-VOLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR AND VOLTAGE MONITOR |

| ASC7531AM10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LOW-VOLTAGE 1-WIRE DIGITAL TEMPERATURE SENSOR AND VOLTAGE MONITOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。