- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19892 > AT17F080-30TQC (Atmel)IC FLASH CONFIG 8M 44TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AT17F080-30TQC |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 16/19頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FLASH CONFIG 8M 44TQFP |

| 標(biāo)準(zhǔn)包裝: | 100 |

| 可編程類型: | 閃存 |

| 存儲(chǔ)容量: | 8Mb |

| 電源電壓: | 2.97 V ~ 3.63 V |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 44-TQFP |

| 供應(yīng)商設(shè)備封裝: | 44-TQFP(10x10) |

| 包裝: | 托盤 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

6

3039K–CNFG–2/08

AT17F040/080

5.4

PAGESEL[1:0](2)

Page select inputs. Used to determine which of the 4 memory pages are targeted during a serial

configuration download. The address space for each of the pages is shown in Table 5-2. When

SER_EN is Low (ISP mode) these pins have no effect.

5.5

RESET/OE(1)

Output Enable (active High) and RESET (active Low) when SER_EN is High. A Low level on

RESET/OE resets both the address and bit counters. A High level (with CE Low) enables the

data output driver.

5.6

CE(1)

Chip Enable input (active Low). A Low level (with OE High) allows CLK to increment the address

counter and enables the data output driver. A High level on CE disables both the address and bit

counters and forces the device into a low-power standby mode. Note that this pin will not

enable/disable the device in the 2-wire Serial Programming mode (SER_EN Low).

5.7

GND

Ground pin. A 0.2 F decoupling capacitor between V

CC and GND is recommended.

5.8

CEO

Chip Enable Output (when SER_EN is High). This output goes Low when the internal address

counter has reached its maximum value. If the PAGE_EN input is set High, the maximum value

is the highest address in the selected partition. The PAGESEL[1:0] inputs are used to make the

4 partition selections. If the PAGE_EN input is set Low, the device is not partitioned and the

address maximum value is the highest address in the device, see Table 5-2 on page 6. In a

daisy chain of AT17F Series devices, the CEO pin of one device must be connected to the CE

input of the next device in the chain. It will stay Low as long as CE is Low and OE is High. It will

then follow CE until OE goes Low; thereafter, CEO will stay High until the entire EEPROM is

read again.

Notes:

1. This pin has an internal 20 k

pull-up resistor.

2. This pin has an internal 30 k

pull-down resistor.

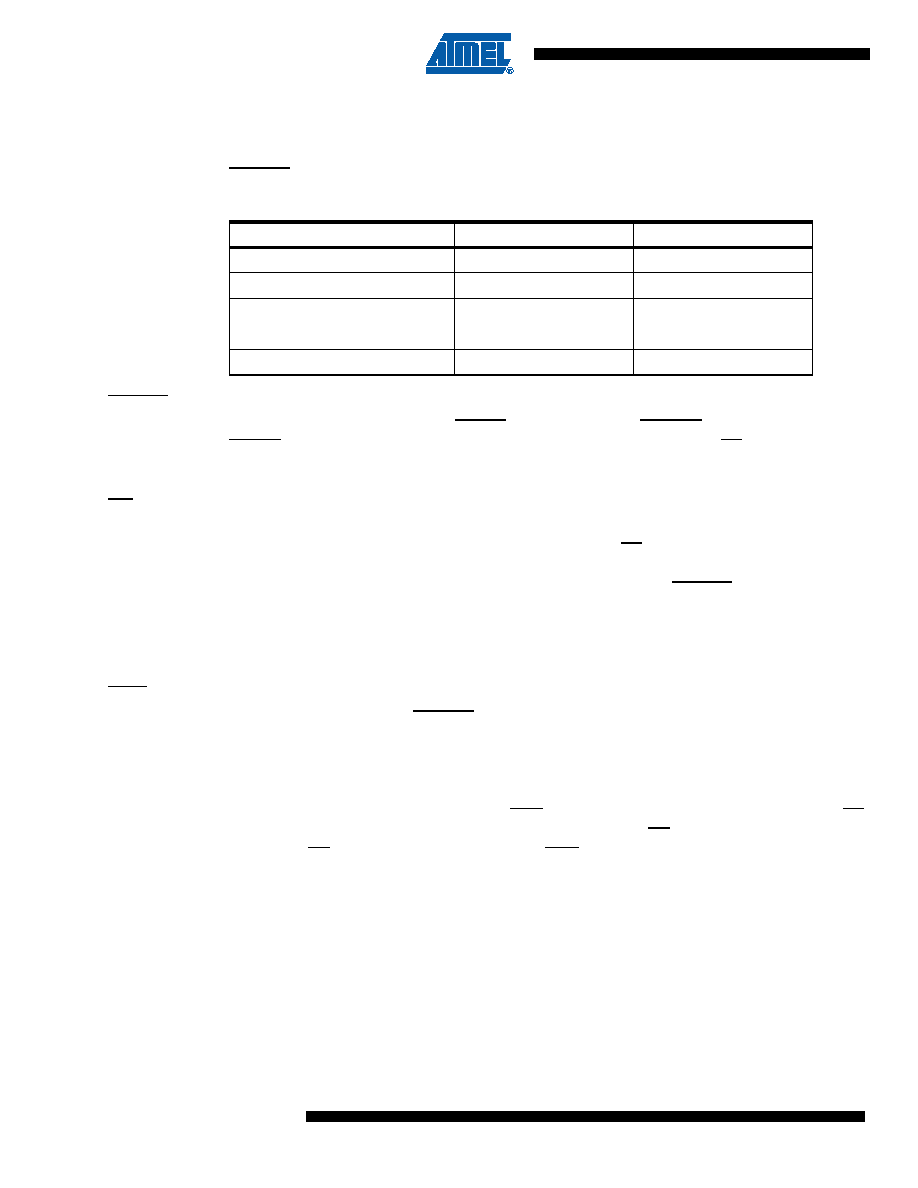

Table 5-2.

Address Space

Paging Decodes

AT17F040 (4 Mbits)

AT17F080 (8 Mbits)

PAGESEL = 00, PAGE_EN = 1

00000 – 0FFFFh

00000 – 1FFFFh

PAGESEL = 01, PAGE_EN = 1

10000 – 1FFFFh

20000 – 3FFFFh

PAGESEL = 10, PAGE_EN = 1

20000 – 2FFFFh

40000 – 5FFFFh

PAGESEL = 11, PAGE_EN = 1

30000 – 3FFFFh

60000 – 7FFFFh

PAGESEL = XX, PAGE_EN = 0

00000 – 3FFFFh

00000 – 7FFFFh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FT531AA | IC REG LDO 1.2V SOT23-5 |

| T97E227K016EBB | CAP TANT 220UF 16V 10% 2917 |

| TPSD476K025R0150 | CAP TANT 47UF 25V 10% 2917 |

| T86D106K035EBBL | CAP TANT 10UF 35V 10% 2917 |

| AT17F040A-30QI | IC FLASH CONFIG 4M 32TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT17F080-30TQI | 功能描述:FPGA-配置存儲(chǔ)器 FPGA SERIAL CONFIG 30MHZ 3.3V IND TEMP RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| AT17F080A-30CU | 功能描述:FPGA-配置存儲(chǔ)器 SER CONFIG FLASH-8M ALTERA PINOUT-30MHZ RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| AT17F080A-30JC | 功能描述:FPGA-配置存儲(chǔ)器 Serial Flash RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| AT17F080A-30JI | 功能描述:FPGA-配置存儲(chǔ)器 Serial Flash RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

| AT17F080A-30JU | 功能描述:FPGA-配置存儲(chǔ)器 SER CONFIG FLASH-8M ALTERA PINOUT-30MHZ RoHS:否 制造商:Altera Corporation 存儲(chǔ)類型:Flash 存儲(chǔ)容量:1.6 Mbit 工作頻率:10 MHz 電源電壓-最大:5.25 V 電源電壓-最小:3 V 電源電流:50 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PLCC-20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。