- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3977 > AT22LV10-20PI (Atmel)IC PLD 20NS OTP 24DIP PDF資料下載

參數(shù)資料

| 型號(hào): | AT22LV10-20PI |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 10/12頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC PLD 20NS OTP 24DIP |

| 標(biāo)準(zhǔn)包裝: | 15 |

| 系列: | 22V10 |

| 可編程類型: | EPLD |

| 宏單元數(shù): | 10 |

| 輸入電壓: | 3V |

| 速度: | 20ns |

| 安裝類型: | 通孔 |

| 封裝/外殼: | 24-DIP(0.300",7.62mm) |

| 供應(yīng)商設(shè)備封裝: | 24-PDIP |

| 包裝: | 管件 |

| 其它名稱: | AT22LV1020PI |

AT22LV10(L)

7

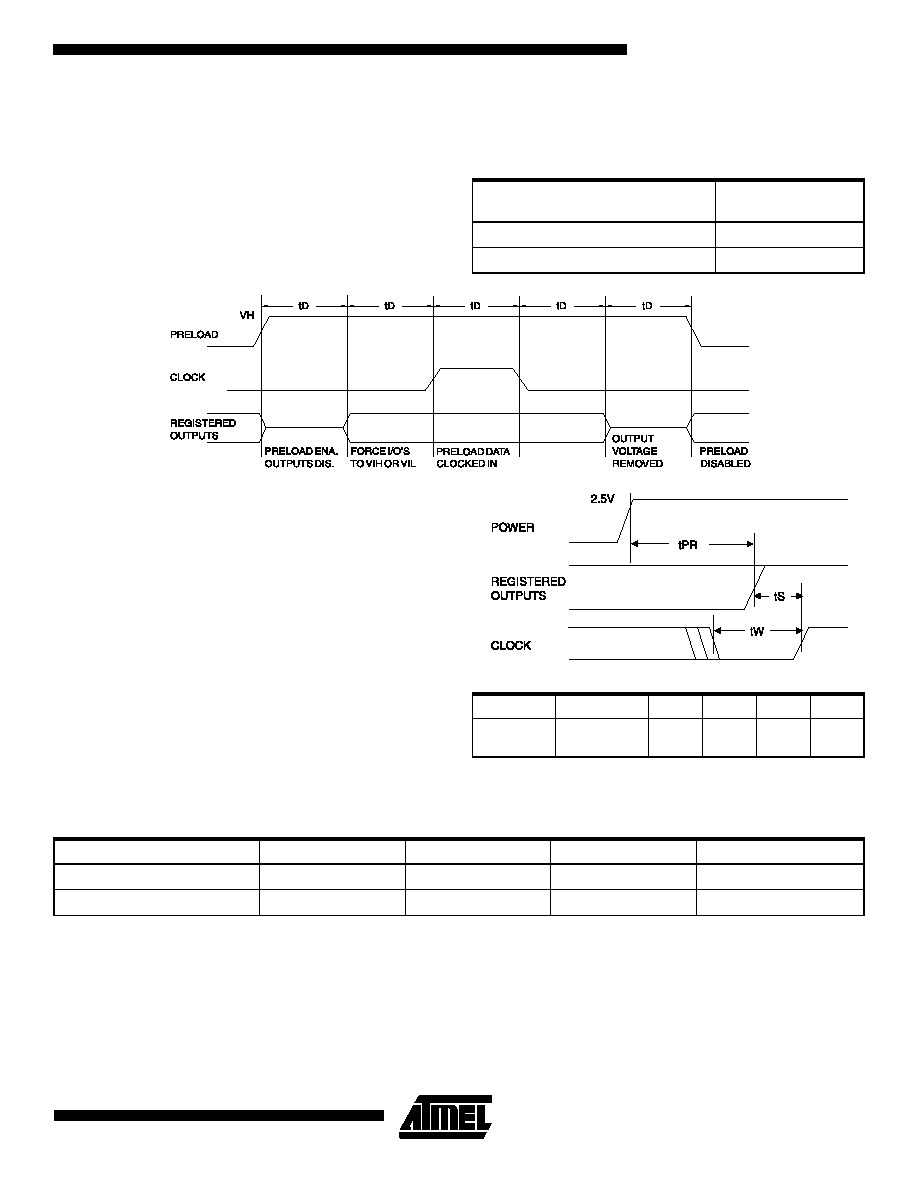

Preload of Registered Outputs

The registers in the AT22LV10 and AT22LV10L are pro-

vided with circuitry to allow loading of each register

asynchronously with either a high or a low. This feature will

simplify testing since any state can be forced into the regis-

ters to control test sequencing. A V

IH level on the I/O pin

will force the register high; a V

IL will force it low, indepen-

dent of the polarity bit (C0) setting. The preload state is

entered by placing an 11.5V to 13V signal on pin 8 on

DIPs, and pin 10 on SMPs. When the clock pin is pulsed

high, the data on the I/O pins is placed into the ten

registers.

Power-up Reset

The registers in the AT22LV10 and AT22LV10L are

designed to reset during power-up. At a point delayed

slightly from V

CC crossing 2.5V, all registers will be reset to

the low state. The output state will depend on the polarity of

the output buffer.

This feature is critical for state machine initialization.

However, due to the asynchronous nature of reset and the

uncertainty of how V

CC actually rises in the system, the

following conditions are required:

1.

The V

CC rise must be monotonis;

2.

After reset occurs, all input and feedback setup

times must be met before driving the clock pin high,

and

3.

The clock must remain stable during t

PR.

Note:

1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

Erasure Characteristics

The entire fuse array of an AT22LV10 or AT22LV10L is

erased after exposure to ultraviolet light at a wavelength of

2537 . Complete erasure is assured after a minimum of

20 minutes exposure using 12,000 W/cm

2 intensity lamps

spaced one inch away from the chip. Minimum erase time

for lamps at other intensity ratings can be calculated from

the minimum integrated erasure dose of 15 Wsec/cm

2. To

prevent unintentional erasure, an opaque label is recom-

mended to cover the clear window on any UV erasable

PLD which will be subjected to continuous fluorescent

indoor lighting or sunlight.

Level Forced on Registered Output

Pin During Preload Cycle

Register State After

Cycle

V

IH

High

V

IL

Low

Parameter

Description

Min

Typ

Max

Units

t

PR

Power-up

Reset Time

600

1000

ns

Pin Capacitance

(f = 1 MHz, T = 25°C)

(1)

Typ

Max

Units

Conditions

C

IN

58

pF

V

IN = 0V

COUT

68

pF

VOUT = 0V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC000EI10R | IC MPU 32BIT 10MHZ 64-PLCC |

| MC68HC000CRC8 | IC MPU 32BIT 8MHZ 68-PGA |

| MC68HC000CRC16 | IC MPU 32BIT 16MHZ 68-PGA |

| MC68HC000CRC12 | IC MPU 32BIT 12MHZ 68-PGA |

| MC68HC000CRC10 | IC MPU 32BIT 10MHZ 68-PGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT22LV10-20SC | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Voltage UV Erasable Programmable Logic Device |

| AT22LV10-20SI | 功能描述:IC PLD 20NS OTP SO-24 RoHS:否 類別:集成電路 (IC) >> 嵌入式 - PLD(可編程邏輯器件) 系列:22V10 標(biāo)準(zhǔn)包裝:46 系列:- 可編程類型:PAL FLASH 宏單元數(shù):8 輸入電壓:5V 速度:15ns 安裝類型:表面貼裝 封裝/外殼:20-LCC(J 形引線) 供應(yīng)商設(shè)備封裝:20-PLCC(9x9) 包裝:管件 其它名稱:428-1277 |

| AT22LV10-20YC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| AT22LV10-20YI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| AT22LV10-20YM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。