- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362469 > AT25F1024C1-10CI-2.7 SPI Serial EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | AT25F1024C1-10CI-2.7 |

| 英文描述: | SPI Serial EEPROM |

| 中文描述: | SPI串行EEPROM |

| 文件頁(yè)數(shù): | 8/17頁(yè) |

| 文件大小: | 239K |

| 代理商: | AT25F1024C1-10CI-2.7 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

8

AT25F1024

1440D

–

02/01

READ PRODUCT ID (RDID):

The RDID instruction allows the user to read the manufac-

turer and product ID of the device. The first byte after the instruction will be the

manufacturer code (1FH = ATMEL), followed by the device code.

WRITE STATUS REGISTER (WRSR):

The WRSR instruction allows the user to select

one of four levels of protection. The AT25F1024 is divided into four sectors. Top quarter

(1/4), top half (1/2), or all of the memory sectors can be protected (locked out) from

write. Any of the locked-out sectors will therefore be READ only. The locked-out sector

and the corresponding status register control bits are shown in Table 4.

The three bits, BP0, BP1, and WPEN, are nonvolatile cells that have the same proper-

ties and functions as the regular memory cells (e.g., WREN, t

WC

, RDSR).

The WRSR instruction also allows the user to enable or disable the Write Protect (WP)

pin through the use of the Write Protect Enable (WPEN) bit. Hardware write protection is

enabled when the WP pin is low and the WPEN bit is

“

1

”

. Hardware write protection is

disabled when either the WP pin is high or the WPEN bit is

“

0.

”

When the device is hard-

ware write protected, writes to the Status Register, including the Block Protect bits and

the WPEN bit, and the locked-out sectors in the memory array are disabled. Write is

only allowed to sectors of the memory which are not locked out. The WRSR instruction

is self-timed to automatically erase and program BP0, BP1, and WPEN bits. In order to

write the status register, the device must first be write enabled via the WREN instruction.

Then, the instruction and data for the three bits are entered. During the internal write

cycle, all instructions will be ignored except RDSR instructions. The AT25F1024 will

automatically return to write disable state at the completion of the WRSR cycle.

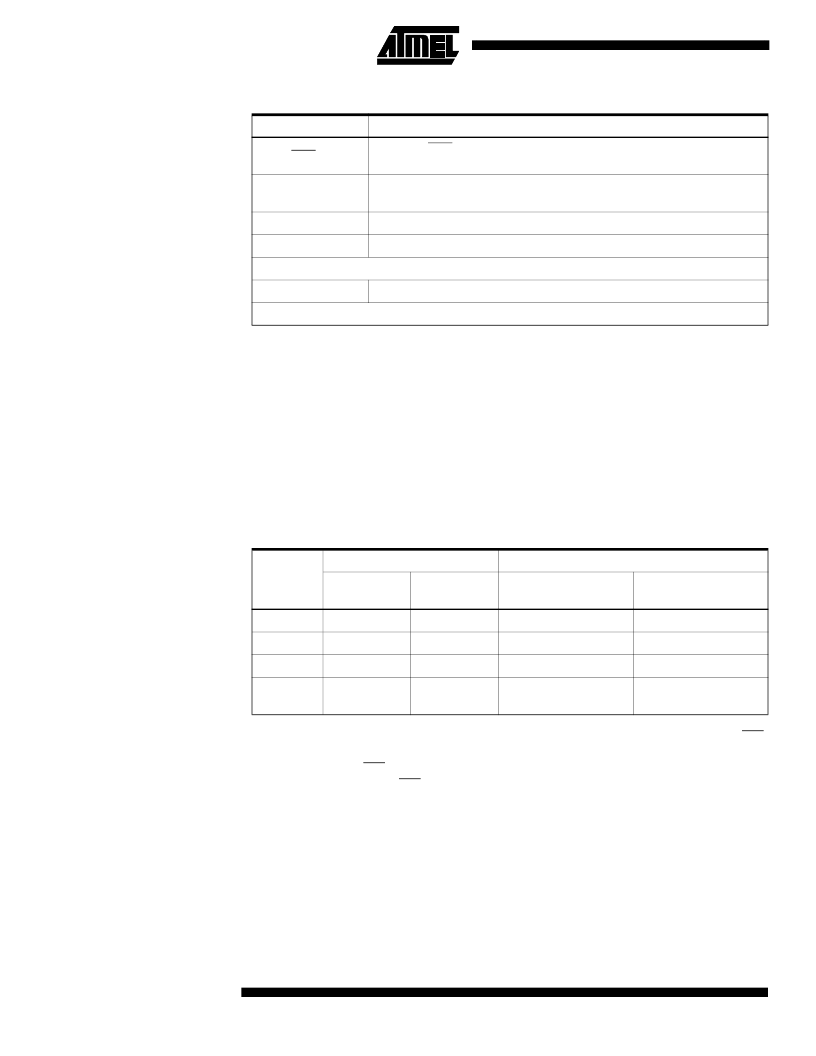

Table 3.

Read Status Register Bit Definition

Bit

Definition

Bit 0 (RDY)

Bit 0 = 0 (RDY) indicates the device is READY. Bit 0 = 1 indicates the

write cycle is in progress.

Bit 1 (WEN)

Bit 1 = 0 indicates the device

is not

WRITE ENABLED. Bit 1 = 1 indicates

the device is WRITE ENABLED.

Bit 2 (BP0)

See Table 4.

Bit 3 (BP1)

See Table 4.

Bits 4-6 are 0s when device is not in an internal write cycle.

Bit 7 (WPEN)

See Table 5.

Bits 0-7 are 1s during an internal write cycle.

Table 4.

Block Write Protect Bits

Level

Status Register Bits

AT25F1024

BP1

BP0

Array Addresses

Locked Out

Locked-out

Sector(s)

0

0

0

None

None

1(1/4)

0

1

018000 - 01FFFF

Sector 4

2(1/2)

1

0

010000 - 01FFFF

Sector 3, 4

3(All)

1

1

000000 - 01FFFF

All sectors

(1 - 4)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT25HP512CI-10CI-1.8 | EEPROM |

| AT25HP512CI-10CI-2.7 | EEPROM |

| AT25HP512W2-10SC | SPI Serial EEPROM |

| AT25HP512W2-10SC-1.8 | SPI Serial EEPROM |

| AT25HP512W2-10SC-2.7 | SPI Serial EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT25F1024N-10SI-2.7 | 制造商:Atmel Corporation 功能描述:Flash Serial-SPI 3V/3.3V 1Mbit 128K x 8bit 20ns 8-Pin SOIC |

| AT25F1024N-10SU-2.7 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:SPI Serial Memory |

| AT25F1024Y4-10YU-2.7 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:SPI Serial Memory |

| AT25F2048 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:SPI Serial Memory 2M (262,144 x 8) |

| AT25F2048_07 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:2Mbit High Speed SPI Serial Flash Memory 2M (262,144 x 8) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。