- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4185 > AT6002-4QC (Atmel)IC FPGA 6K GATE 4NS 132BQFP PDF資料下載

參數(shù)資料

| 型號: | AT6002-4QC |

| 廠商: | Atmel |

| 文件頁數(shù): | 13/28頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 6K GATE 4NS 132BQFP |

| 標準包裝: | 36 |

| 系列: | AT6000(LV) |

| 邏輯元件/單元數(shù): | 1024 |

| 輸入/輸出數(shù): | 96 |

| 門數(shù): | 6000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 132-BQFP 緩沖式 |

| 供應商設備封裝: | 132-BQFP |

| 其它名稱: | AT60024QC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AT6000(LV) Series

20

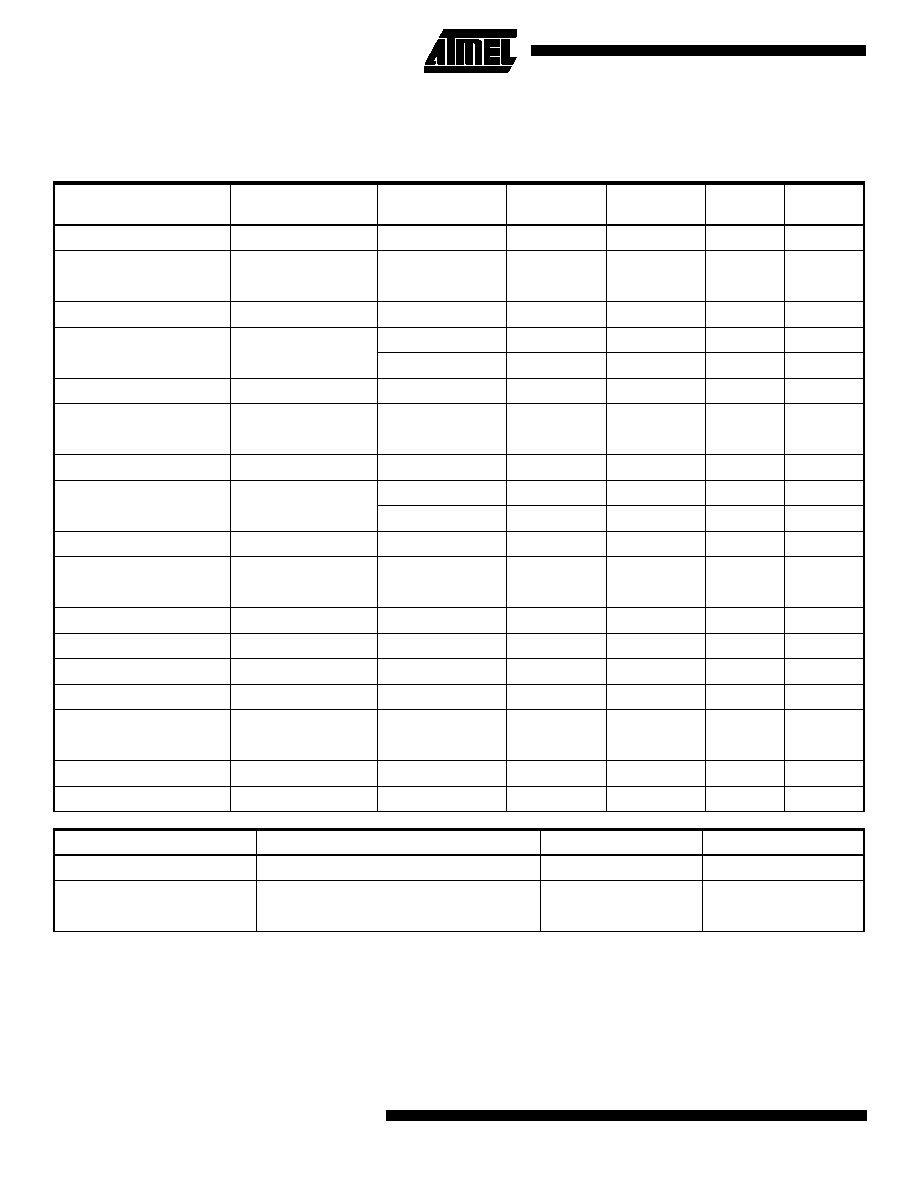

AC Timing Characteristics – 3.3V Operation

Notes:

1. TTL buffer delays are measured from a VIH of 1.5V at the pad to the internal VIH at A. The input buffer load is constant.

2. CMOS buffer delays are measured from a V

IH of 1/2 VCC at the apd to the internal VIH at A. The input buffer load is constant.

3. Buffer delay is to a pad voltage of 1.5V with one output switching.

4. Max specifications are the average of mas t

PDLH and tPDHL.

5. Parameter based on characterization and simulation; not tested in production

6. Exact power calculation is available in an Atmel application note.

7. Load Definition: 1 = Load of one A or B input; 2 = Load of one L input; 3 = Constant Load; 4 = Load of 28 Clock Columns; 5

= Load of 28 Reset Columns; 6 = Tester Load of 50 pF.

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds.

Worst case: V

CC = 3.0V to 3.6V. Temperature = 0°C to 70°C.

Cell Function

Parameter

From

To

Load

Definition

-4

Units

Wire

t

PD (max)

A, B, L

A, B

1

1.8

ns

NAND

tPD (max)

A, B, L

B

1

3.2

ns

XOR

t

PD (max)

A, B, L

A

1

4.0

ns

AND

t

PD (max)

A, B, L

B

1

3.2

ns

MUX

t

PD (max)

A, B

A

1

4.0

ns

LA

1

4.9

ns

D-Flip-flop

t

setup (min)

A, B, L

CLK

-

3.0

ns

D-Flip-flop

thold (min)

CLK

A, B, L

-

0

ns

D-Flip-flop

t

PD (max)

CLK

A

1

3.0

ns

Bus Driver

t

PD (max)

A

L

2

4.0

ns

Repeater

t

PD (max)

L, E

E

3

2.3

ns

L, E

L

2

3.0

ns

Column Clock

t

PD (max)

GCLK, A, ES

CLK

3

3.0

ns

Column Reset

tPD (max)

GRES, A, EN

RES

3

3.0

ns

Clock Buffer

t

PD (max)

CLOCK PIN

GCLK

4

2.9

ns

Reset Buffer

t

PD (max)

RESET PIN

GRES

5

2.8

ns

TTL Input

tPD (max)

I/O

A

3

1.5

ns

CMOS Input

t

PD (max)

I/O

A

3

2.3

ns

Fast Output

t

PD (max)

A

I/O PIN

6

6.0

ns

Slow Output

tPD (max)

A

I/O PIN

6

12.0

ns

Output Disable

t

PXZ (max)

L

I/O PIN

6

5.5

ns

Fast Enable

t

PXZ (max)

L

I/O PIN

6

6.5

ns

Slow Enable

tPXZ (max)

L

I/O PIN

6

12.5

ns

Device

Cell Types

Outputs

I

CC (max)

Cell

Wire, XWire, Half-adder, Flip-flop

A, B

2.3 A/MHz

Bus

Wire, XWire, Half-adder, Flip-flop, Repeater

L

1.3 A/MHz

Column Clock

Column Clock Driver

CLK

20 A/MHz

相關PDF資料 |

PDF描述 |

|---|---|

| AT6002-4JC | IC FPGA 2K GATE 4NS 84PLCC |

| RCB106DHBR-S621 | EDGECARD 212POS DIP R/A .050 SLD |

| AT6002-4AI | IC FPGA 6K GATE 4NS 100VQFP |

| AT6002-4AC | IC FPGA 6K GATE 4NS 100VQFP |

| AT6002-2QI | IC FPGA 2NS 132BQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AT6002-4QI | 功能描述:FPGA - 現(xiàn)場可編程門陣列 ASICS RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6002A-2AC | 功能描述:FPGA - 現(xiàn)場可編程門陣列 6000 GATE - 2NS RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6002A-2AI | 功能描述:FPGA - 現(xiàn)場可編程門陣列 6000 GATE - 2NS RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6002A-4AC | 功能描述:FPGA - 現(xiàn)場可編程門陣列 6000 GATE - 4NS 144 RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6002A-4AI | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA 6000 GATE 4NS IND TEMP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。