- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19626 > ATF2500C-20JI (Atmel)IC CPLD EE 20NS 44PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | ATF2500C-20JI |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 23/24頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CPLD EE 20NS 44PLCC |

| 標(biāo)準(zhǔn)包裝: | 27 |

| 系列: | ATF2500C(L) |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 20.0ns |

| 電壓電源 - 內(nèi)部: | 4.5 V ~ 5.5 V |

| 宏單元數(shù): | 24 |

| 輸入/輸出數(shù): | 24 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 44-PLCC |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)

8

0777K–PLD–1/24/08

ATF2500C

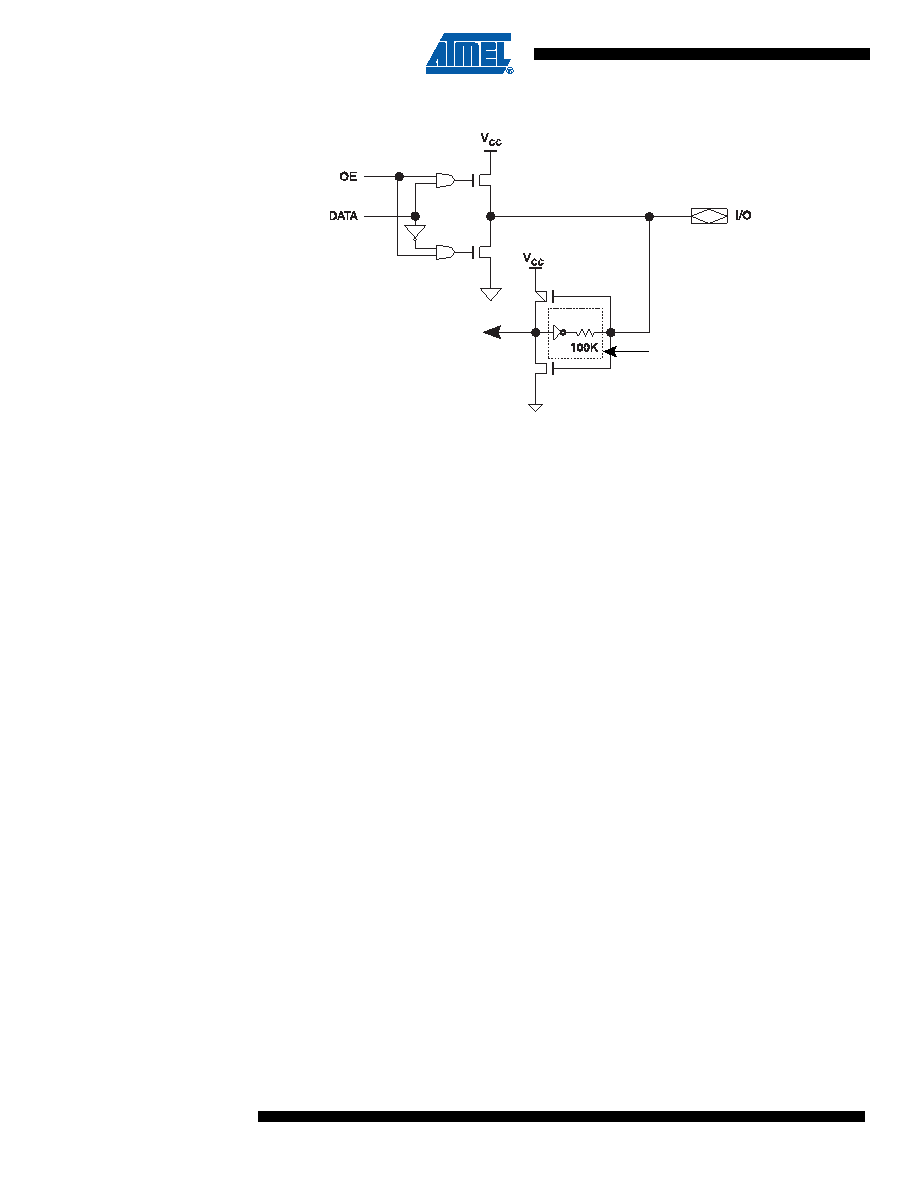

Figure 8-2.

I/O Diagram

9.

Functional Logic Diagram Description

The ATF2500C functional logic diagram describes the interconnections between the input, feed-

back pins and logic cells. All interconnections are routed through the single global bus.

The ATF2500Cs are straightforward and uniform PLDs. The 24 macrocells are numbered 0

through 23. Each macrocell contains 17 AND gates. All AND gates have 172 inputs. The five

lower product terms provide AR1, CK1, CK2, AR2, and OE. These are: one asynchronous reset

and clock per flip-flop, and an output enable. The top 12 product terms are grouped into three

sum terms, which are used as shown in the macrocell diagrams.

Eight synchronous preset terms are distributed in a 2/4 pattern. The first four macrocells share

Preset 0, the next two share Preset 1, and so on, ending with the last two macrocells sharing

Preset 7.

The 14 dedicated inputs and their complements use the numbered positions in the global bus as

shown. Each macrocell provides six inputs to the global bus: (left to right) feedback F2

(1) true

and false, flip-flop Q1 true and false, and the pin true and false. The positions occupied by these

signals in the global bus are the six numbers in the bus diagram next to each macrocell.

Note:

1. Either the flip-flop input (D/T2) or output (Q2) may be fed back in the ATF2500Cs.

INPUT

PROGRAMMABLE

OPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5LV-256/120-10YI | IC CPLD 256MC 120I/O 160PQFP |

| NTA1205MC | CONV DC/DC SM 1W 12VIN 5V DL 1KV |

| SA56004BDP,118 | IC TEMP SENSOR 8-TSSOP |

| V300A2E160BF | CONVERTER MOD DC/DC 2V 160W |

| MIC5239-5.0BM | IC REG LDO 5V .5A 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF2500C-20KM | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 STD PWR 2500 GATE 24 MACROCELL 5V RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20LM | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 ASICS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 2500 GATE 24 MACRO STD PWR 5V-20NS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 2500 GATE 24 MACRO STD PWR 5V-20NS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF2500C-20PU | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 20 ns 24 I/O Pins 24 macorcells 48 reg RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。