- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22100 > ATF750LVC-15JU (Atmel)IC CPLD HS 750 GATE 28-PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | ATF750LVC-15JU |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 12/19頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CPLD HS 750 GATE 28-PLCC |

| 標(biāo)準(zhǔn)包裝: | 38 |

| 系列: | ATF750LVC |

| 可編程類型: | 系統(tǒng)內(nèi)可編程(最少 1K 次編程/擦除循環(huán)) |

| 最大延遲時(shí)間 tpd(1): | 15.0ns |

| 電壓電源 - 內(nèi)部: | 3 V ~ 5.5 V |

| 宏單元數(shù): | 10 |

| 輸入/輸出數(shù): | 10 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 28-PLCC(11.51x11.51) |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

2

1447F–PLD–11/08

ATF750LVC

3.

Pin Configurations

Each of the ATF750LVC’s 22 logic pins can be used as an input. Ten of these can be used as

inputs, outputs or bi-directional I/O pins. Each flip-flop is individually configurable as either

D- or T-type. Each flip-flop output is fed back into the array independently. This allows burying

of all the sum terms and flip-flops.

There are 171 total product terms available. There are two sum terms per output, providing

added flexibility. A variable format is used to assign between four to eight product terms per

sum term. Much more logic can be replaced by this device than by any other 24-pin PLD. With

20 sum terms and flip-flops, complex state machines are easily implemented with logic to

spare.

Product terms provide individual clocks and asynchronous resets for each flip-flop. Each flip-

flop may also be individually configured to have direct input pin controlled clocking. Each out-

put has its own enable product term. One product term provides a common synchronous

preset for all flip-flops. Register preload functions are provided to simplify testing. All registers

automatically reset upon power-up.

Pin Name

Function

CLK

Clock

IN

Logic Inputs

I/O

Bi-directional Buffers

GND

Ground

VCC

3V to 5.5V Supply

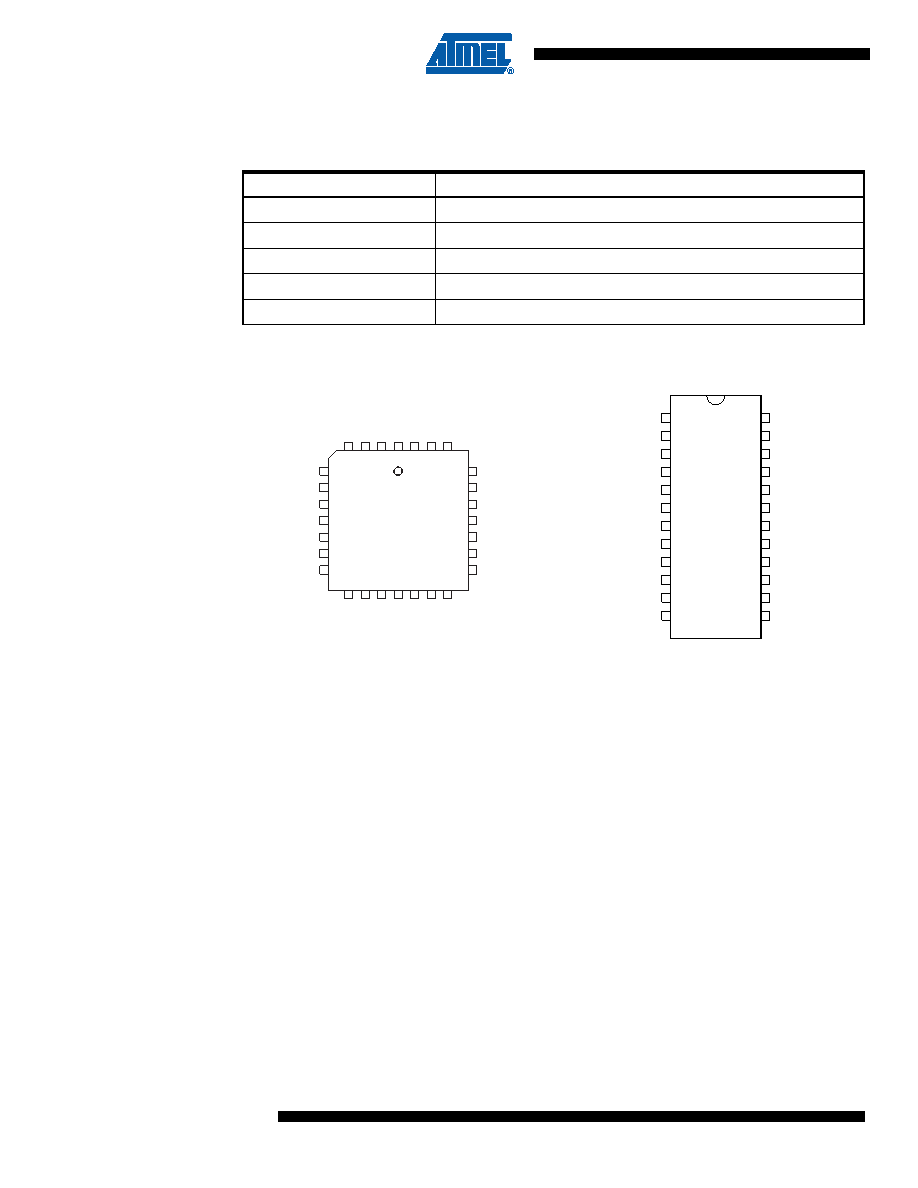

3.1

PLCC

Note:

1. For PLCC, pins 1, 8, 15, and 22 can

be left unconnected. For superior

performance, connect VCC to pin 1

and GND to pins 8, 15, and 22.

3.2

DIP/SOIC/TSSOP

5

6

7

8

9

10

11

25

24

23

22

21

20

19

IN

GND(1)

IN

I/O

GND(1)

I/O

4

3

2

1

2

8

27

26

12

1

3

14

15

16

17

1

8

IN

GND

(1)

IN

I/O

IN

CLK/IN

VCC

(1)

VCC

I/O

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

CLK/IN

IN

GND

VCC

I/O

IN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATF750CL-15XU | IC PLD HS 750 GATE 5.0V 24-TSSOP |

| VE-273-CY-F2 | CONVERTER MOD DC/DC 24V 50W |

| ATF750CL-15SU | IC PLD HS 750 GATE 5.0V 24-SOIC |

| TAP224M035DTW | CAP TANT 0.22UF 35V 20% RADIAL |

| ATF750CL-15PU | IC PLD HS 750 GATE 5.0V 24-PDIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATF750LVC-15PC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 750 GATE LOW POWER - 15NS 24 RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF750LVC-15PI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 750 GATE LOW POWER - 15NS 24 RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF750LVC-15PU | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 750 GATE LOW POWER - 15NS RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF750LVC-15SC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 750 GATE LOW POWER - 15NS 24 RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| ATF750LVC-15SI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 750 GATE LOW POWER - 15NS 24 RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。