- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295120 > AX250-FG256X79 FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | AX250-FG256X79 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA256 |

| 封裝: | 1 MM PITCH, FBGA-256 |

| 文件頁數(shù): | 24/230頁 |

| 文件大小: | 6485K |

| 代理商: | AX250-FG256X79 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁

Axcelerator Family FPGAs

1- 6

v2.8

operating with input frequencies ranging from 14 MHz

to 200 MHz and can generate output frequencies

between 20 MHz and 1 GHz. The clock can be either

divided or multiplied by factors ranging from 1 to 64.

Additionally, multiply and divide settings can be used in

any combination as long as the resulting clock frequency

is between 20 MHz and 1 GHz. Adjacent PLLs can be

cascaded to create complex frequency combinations.

The PLL can be used to introduce either a positive or a

negative clock delay of up to 3.75 ns in 250 ps

increments. The reference clock required to drive the PLL

can be derived from three sources: external input pad

(either single-ended or differential), internal logic, or the

output of an adjacent PLL.

Low Power (LP) Mode

The AX architecture was created for high-performance

designs but also includes a low power mode (activated via

the LP pin). When the low power mode is activated, I/O

banks can be disabled (inputs disabled, outputs tristated),

and PLLs can be placed in a power-down mode. All

internal register states are maintained in this mode.

Furthermore, individual I/O banks can be configured to

opt out of the LP mode, thereby giving the designer access

to critical signals while the rest of the chip is in low power

mode.

The power can be further reduced by providing an

external voltage source (VPUMP) to the device to bypass

the internal charge pump (See "Low Power Mode" on

page 2-89 for more information).

Design Environment

The Axcelerator family of FPGAs is fully supported by both

Actel's Libero Integrated Design Environment and

Designer FPGA Development software. Actel Libero IDE is

an integrated design manager that seamlessly integrates

design tools while guiding the user through the design

flow, managing all design and log files, and passing

necessary design data among tools. Additionally, Libero

IDE allows users to integrate both schematic and HDL

synthesis into a single flow and verify the entire design in

a single environment (see the Libero IDE Flow diagram

located on Actel’s website). Libero IDE includes Synplify

Actel Edition (AE) from Synplicity, ViewDraw AE from

Mentor Graphics, ModelSim HDL Simulator from

Mentor

Graphics,

WaveFormer

Lite

AE

from

SynaptiCAD, and Designer software from Actel.

Actel's Designer software is a place-and-route tool and

provides a comprehensive suite of backend support tools

for FPGA development. The Designer software includes

the following:

Timer – a world-class integrated static timing analyzer

and constraints editor which support timing-driven

place-and-route

NetlistViewer – a design netlist schematic viewer

ChipPlanner – a graphical floorplanner viewer and editor

SmartPower – allows the designer to quickly estimate

the power consumption of a design

PinEditor – a graphical application for editing pin

assignments and I/O attributes

I/O Attribute Editor – displays all assigned and

unassigned I/O macros and their attributes in a

spreadsheet format

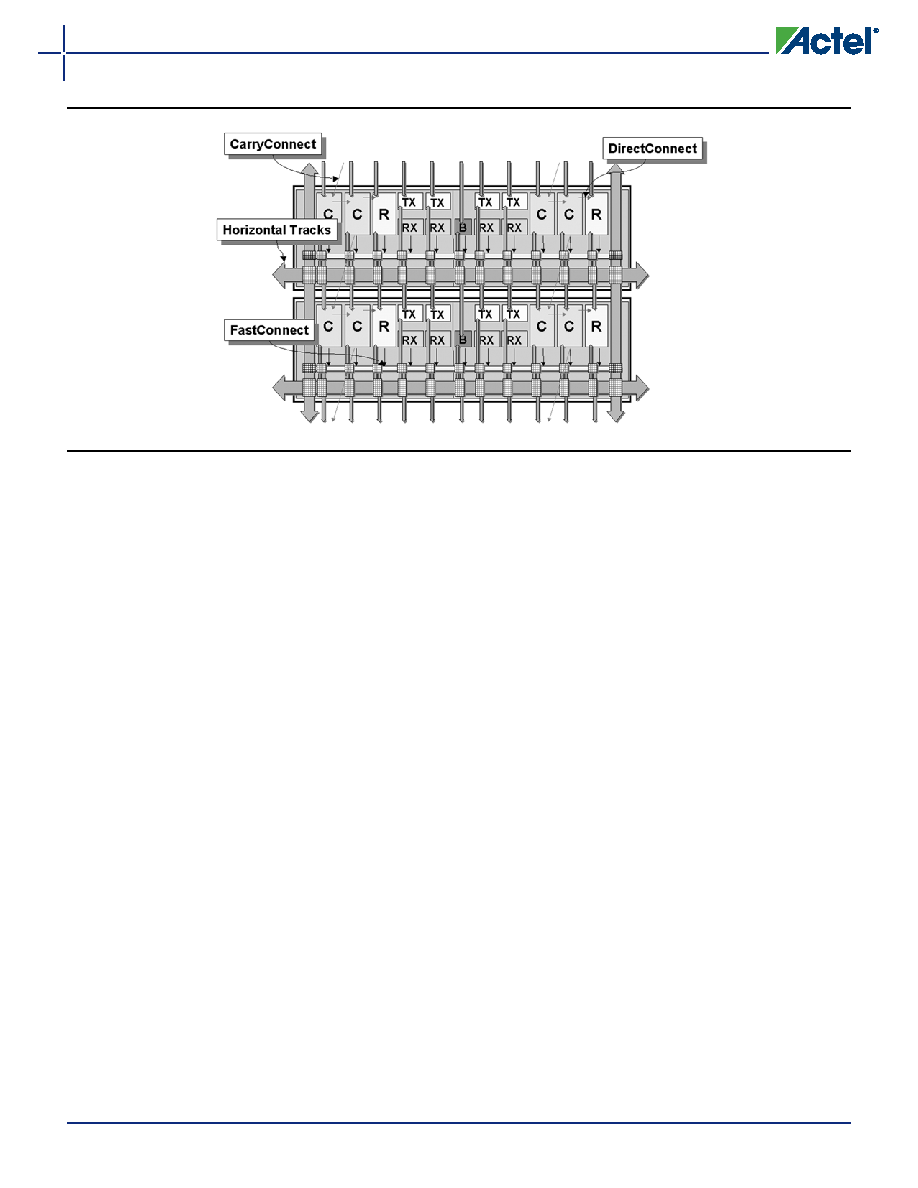

Figure 1-8 AX Routing Structures

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AX250-FG256 | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA256 |

| AX250-FG484IX79 | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA484 |

| AX250-FG484I | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA484 |

| AX250-FG484MX79 | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA484 |

| AX250-FG484M | FPGA, 2816 CLBS, 154000 GATES, 649 MHz, PBGA484 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AX250-FG484 | 功能描述:IC FPGA AXCELERATOR 250K 484FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Axcelerator 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| AX250-FG484I | 功能描述:IC FPGA AXCELERATOR 250K 484FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Axcelerator 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| AX250-FG484M | 制造商:Microsemi Corporation 功能描述:FPGA AXCELERATOR 154K GATES 2816 CELLS 649MHZ 0.15UM 1.5V 48 - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 248 I/O 484FBGA |

| AX250-FG896 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:Axcelerator Family FPGAs |

| AX250-FG896B | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:Axcelerator Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。