- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295167 > BS616LV4020BC (BRILLIANCE SEMICONDUCTOR, INC.) Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable PDF資料下載

參數(shù)資料

| 型號(hào): | BS616LV4020BC |

| 廠商: | BRILLIANCE SEMICONDUCTOR, INC. |

| 元件分類: | SRAM |

| 英文描述: | Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| 中文描述: | 非常低功率/電壓CMOS SRAM的256K × 16或512K × 8位開關(guān) |

| 文件頁數(shù): | 7/8頁 |

| 文件大小: | 255K |

| 代理商: | BS616LV4020BC |

Revision 2.1

Jan.

2004

7

R0201-BS616LV1611

BSI

BS616LV1611

NOTES:

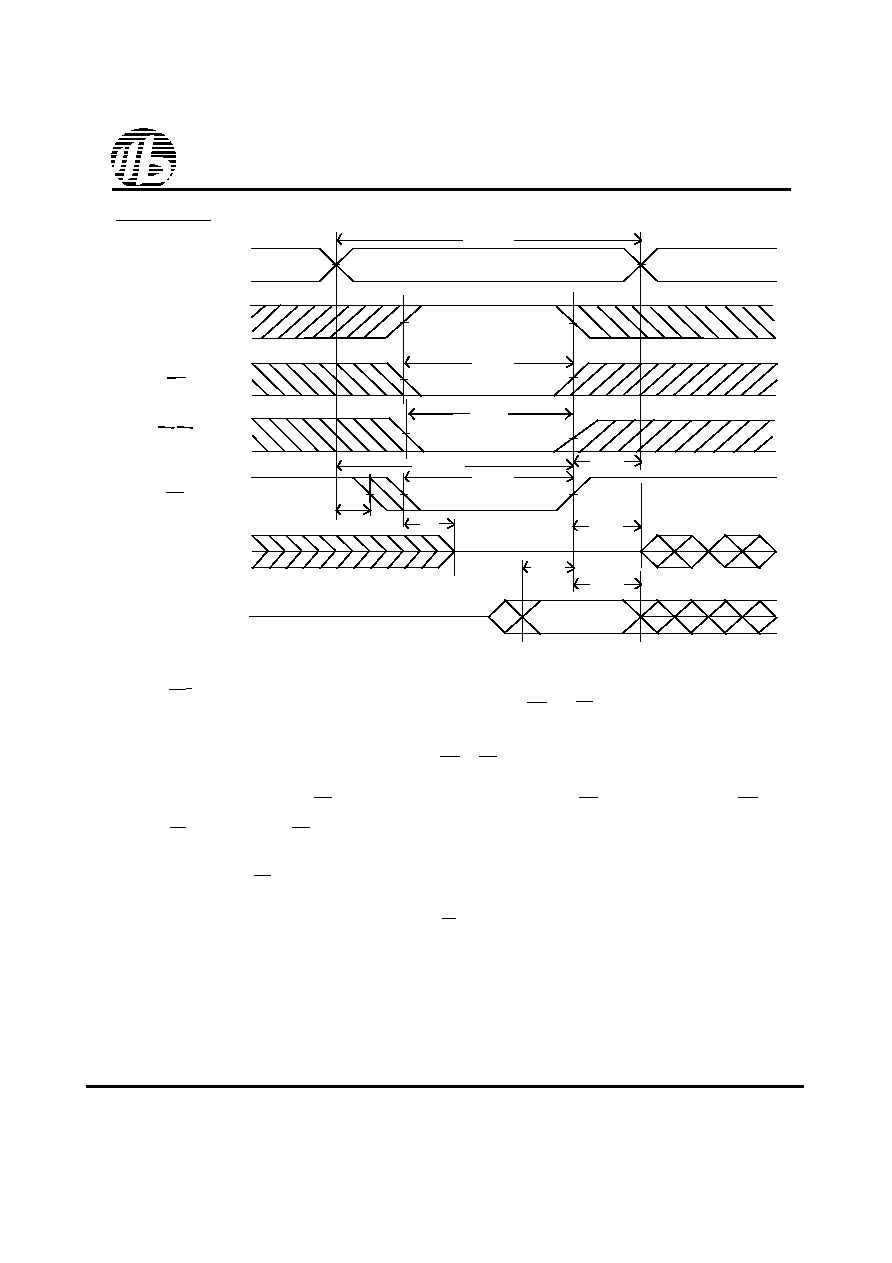

1. WE must be high during address transitions.

2. The internal write time of the memory is defined by the overlap of CE2, CE1 and WE low. All signals

must be active to initiate a write and any one signal can terminate a write by going inactive.

The data input setup and hold timing should be referenced to the second transition edge of

the signal that terminates the write.

3. TWR is measured from the earlier of CE2 going low, or CE1 or WE going high at the end of write cycle.

4. During this period, DQ pins are in the output state so that the input signals of opposite phase

to the outputs must not be applied.

5. If the CE2 high transition or CE1 low transition occurs simultaneously with the WE low transitions or after the WE

transition, output remain in a high impedance state.

6. OE is continuously low (OE = VIL ).

7. DOUT is the same phase of write data of this write cycle.

8. DOUT is the read data of next address.

9. If CE2 is high or CE1 is low during this period, DQ pins are in the output state. Then the data input signals of

opposite phase to the outputs must not be applied to them.

10. The parameter is guaranteed but not 100% tested.

11. TCW is measured from the later of CE2 going high or CE1 going low to the end of write.

WRITE CYCLE2 (1,6)

t WC

t CW

(11)

(2)

t WP

t AW

t WHZ

(4,10)

t AS

t WR

(3)

t DH

t DW

D

IN

D

OUT

WE

CE1

ADDRESS

t OW

(7)

(8)

(8,9)

CE2

LB,UB

t BW

(5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BS616UV4020BC | Ultra Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| BS616UV2019AC | Ultra Low Power/Voltage CMOS SRAM 128K X 16 bit |

| BS616UV2019ACP10 | Hex Buffer/Driver With Open-Drain Outputs 14-TVSOP -40 to 85 |

| BS616UV2019ACP85 | Hex Buffer/Driver With Open-Drain Outputs 14-TVSOP -40 to 85 |

| BS616UV2019AI | Hex Buffer/Driver With Open-Drain Outputs 14-TVSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BS616LV4020BI | 制造商:BSI 制造商全稱:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| BS616LV4020DC | 制造商:BSI 制造商全稱:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| BS616LV4020DI | 制造商:BSI 制造商全稱:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| BS616LV4021 | 制造商:BSI 制造商全稱:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

| BS616LV4021BC | 制造商:BSI 制造商全稱:Brilliance Semiconductor 功能描述:Very Low Power/Voltage CMOS SRAM 256K x 16 or 512K x 8 bit switchable |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。