- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166523 > BU-61582F2-470L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 PDF資料下載

參數(shù)資料

| 型號: | BU-61582F2-470L |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| 封裝: | CERAMIC, DFP-70 |

| 文件頁數(shù): | 24/48頁 |

| 文件大?。?/td> | 378K |

| 代理商: | BU-61582F2-470L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

30

Data Device Corporation

www.ddc-web.com

BU-61582

G-08/02-250

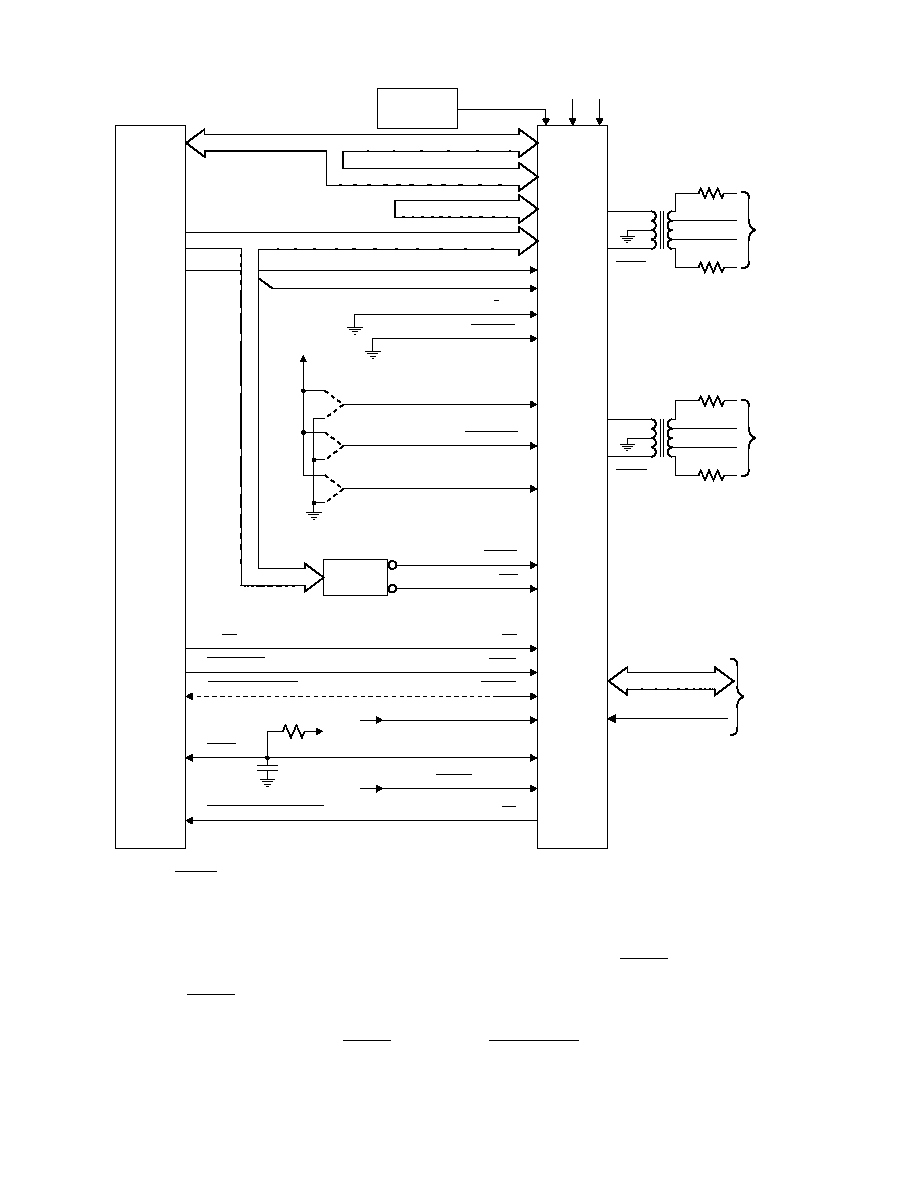

HOST

SP'ACE

55

55

8

7

5

4

1

2

3

CH. A

TX/RXA

55

55

8

7

5

4

1

2

3

CH. B

TX/RXB

RTAD4-RTAD0

RT

ADDRESS,

PARITY

RTADP

D15-D8

+5V

-12V/-15V

CLK IN

16 MHz

CLOCK

OSCILLATOR

POLARITY_SEL

(NOTE 3)

ZERO_WAIT

(NOTE 4)

ADDRESS

DECODER

SELECT

MEM/REG

RD/WR

STRBD

READYD

TAG_CLK

RD/WR

CPU STROBE

CPU ACKNOWLEDGE

(NOTE 6)

RESET

NOTES:

+5V

MSTCLR

SSFLAG/EXT_TRIG

INT

CPU INTERRUPT REQUEST

TRANSFERS ARE TRIGGERED BY THE MOST SIGNIFICANT

BYTE TRANSFER READ ACCESSES AND BY THE

LEAST SIGNIFICANT BYTE TRANSFER FOR WRITE ACCESSES.

IF TRIGGER_SEL = "0", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE LEAST SIGNIFICANT

BYTE TRANSFER FOR READ ACCESSES AND BY THE MOST

SIGNIFICANT BYTE TRANSFER FOR WRITE ACCESSES.

FOR ZERO WAIT INTERFACE (ZERO WAIT = "0"):

IF TRIGGER_SEL = "1", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE LEAST SIGNIFICANT

BYTE TRANSFER, FOR BOTH READ AND WRITE ACCESSES.

IF TRIGGER_SEL = "0", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE MOST SIGNIFICANT

BYTE TRANSFER, FOR BOTH READ AND WRITE ACCESES.

6. CPU ACKNOWLEDGE PROCESSOR INPUT ONLY FOR NON-ZERO

WAIT TYPE OF INTERFACE.

1. CPU D7-D0 CONNECTS TO BOTH D15-D8 AND

D7-D0.

2. CPU ADDRESS LATCH SIGNAL PROVIDED BY PROCESSORS

WITH MULTIPLEXED ADDRESS/DATA BUFFERS.

3. IF POLARITY_SEL = "1", THEN MSB/LSB SELECTS THE MOST

SIGNIFICANT BYTE WHEN LOW, AND THE LEAST

SIGNIFICANT BYTE WHEN HIGH.

SIGNIFICANT BYTE WHEN LOW, AND THE MOST

SIGNIFICANT BYTE WHEN HIGH.

4. ZERO WAIT SHOULD BE STRAPPED TO LOGIC "1" FOR

NON-ZERO WAIT INTERFACE AND TO LOGIC "0" FOR

ZERO WAIT INTERFACE.

5. OPERATION OF TRIGGER_SELECT INPUT IS AS FOLLOWS:

FOR NON-ZERO WAIT INTERFACE (ZERO WAIT = "1"):

IF TRIGGER_SEL = "1", THEN INTERNAL 16-BIT

A15-A12

A11-A0

N/C

ADDR_LAT

CPU ADDRESS LATCH

(NOTE 1)

16/8_BIT

TRANSPARENT/BUFFERED

+5V

CPU D7-D0

(NOTE 2)

A12-A1

CPU A12-A0

MSB/LSB

CPU A0

TRIGGER_SEL

(NOTE 5)

D7-D0

FIGURE 14. 8-BIT BUFFERED MODE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61582F3-130W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61582F3-141K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61582F3-151K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61582F3-160Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61582F3-190S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61585 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61586 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU61586V6-300 | 制造商:DDC 功能描述:MIL-STD-1553/ARINC BUS CONTROLLER/RTU, 70 Pin, Flat Pack |

| BU-61588 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

| BU-61588F0 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。