- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166576 > BU-61703F3-170L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號: | BU-61703F3-170L |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | CERAMIC, QFP-72 |

| 文件頁數(shù): | 52/54頁 |

| 文件大小: | 576K |

| 代理商: | BU-61703F3-170L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁

7

Data Device Corporation

www.ddc-web.com

BU-61703/61705

D1 web-09/02-0

L-BRO

T/R

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

PROM / RAM / PLD

(4Kx1)

SA1

WC/MC/CWC3

WC/MC/CWC2

SA0

WC/MC/CWC4

WC/MC/CWC1

SA4

SA3

SA2

WC/MC/CWC0

I LLEG AL

A0

D0

BU - 61703 / 5

"SSRT"

(400ns max)

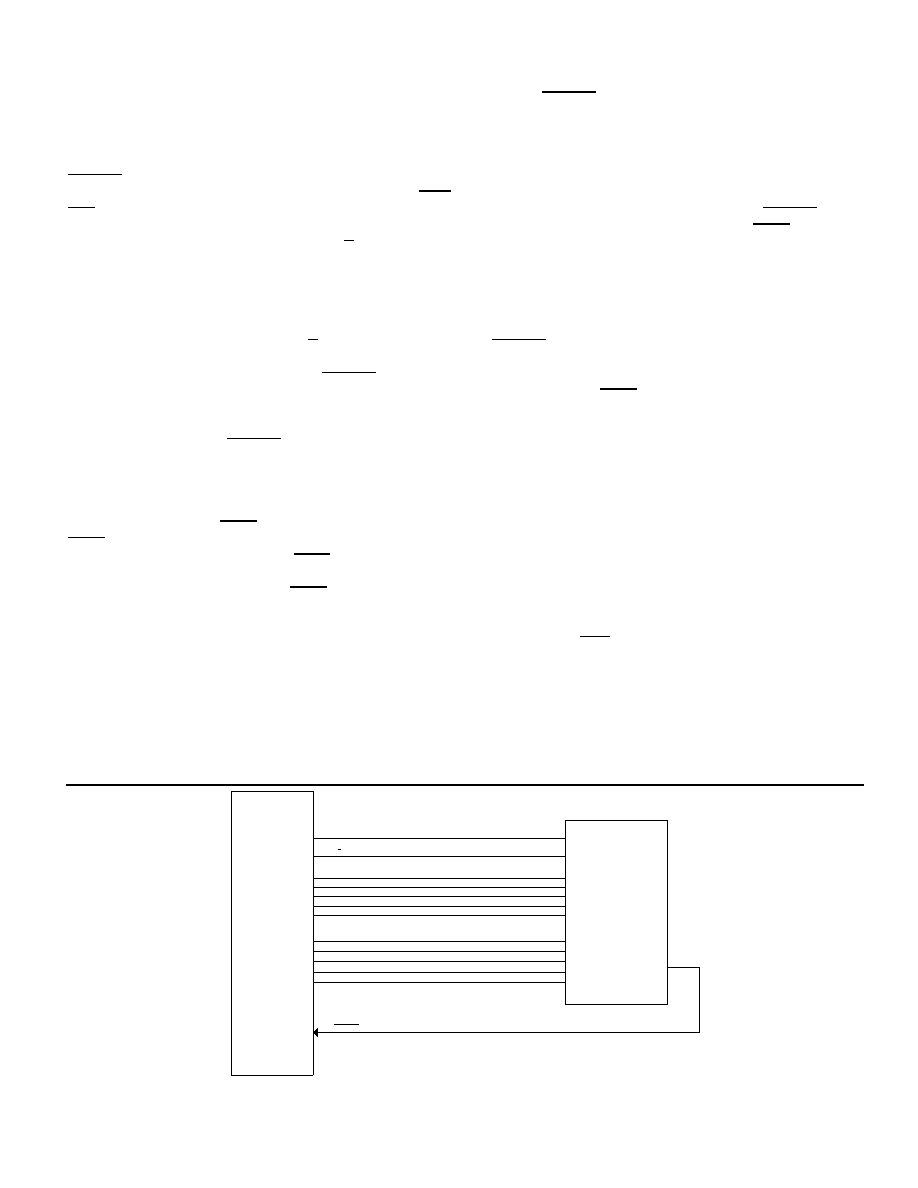

FIGURE 2. BU-61703/5 ILLEGALIZATION

words will be transmitted in response to an illegalized transmit

command. However, data words associated with an illegalized

receive command will be written to the external subsystem

(although these transfers may be blocked using external logic).

ILLEGAL is sampled approximately 2 s following the mid-parity

bit zero crossing of the received command word. A low on ILLE-

GAL will illegalize a particular command word and cause the

SSRT to respond with its Message error bit set in its status word.

Command illegalization based on broadcast, T/R bit, subaddress,

and/or word count/mode code may be implemented by means of

an external PROM, PLD, or RAM device, as shown in FIGURE 2.

The external device may be used to define the legality of specific

commands. Any subset of the possible 1553 commands may be

illegalized as a function of broadcast, T/R bit, subaddress, word

count, and/or mode code. The output of the illegalization device

should be tied directly to the BU-61703/5's ILLEGAL signal input.

The maximum access time of the external illegalizing device is 400

ns.

If illegalization is not used, ILLEGAL should be hardwired to logic

"1".

BUSY

The external subsystem may control the SSRT's Busy RT status

word bit by means of the BUSY input signal. The SSRT samples

BUSY approximately 2 s following the mid-parity bit zero cross-

ing of the received Command Word. If BUSY is sampled low for a

particular message, the value of the busy bit transmitted in the

SSRT's status word will be logic "1". If BUSY is sampled high for a

particular message, the value of the busy bit transmitted in the

SSRT's status word will be logic "0".

If the RT responds to a transmit command with a busy bit of logic

"1", the status word will be transmitted, but no data words will be

transmitted by the SSRT. If the SSRT responds to a receive com-

mand with a busy bit of logic "1", data words will be transferred to

the external subsystem (although these may be blocked by means

of external logic).

Similar to ILLEGAL, it is possible to cause the SSRT to respond

with Busy for specific command words (only), by means of an

external PROM, RAM, or PLD device.

TRANSMIT COMMAND (RT-TO-BC TRANSFER)

If the BU-61703/5 receives a valid Transmit command word that

the subsystem determines is legal (input signal ILLEGAL is high)

and the subsystem is not BUSY (input signal BUSY is high), the

BU-61703/5 will initiate a transmit data response following trans-

mission of its status word. This entails a handshake/read cycle for

each data word transmitted, with the number of data words to be

transmitted specified by the word count field of the transmit com-

mand word.

If ILLEGAL is sampled low, the Message Error bit will be set in the

SSRT's status word. No data words will be transmitted following

transmission of the status word to an illegalized transmit com-

mand. A low on the BUSY input will set the busy bit in the Status

Word; in this instance, only the status word will be transmitted, with

no data words.

RECEIVE COMMAND (BC-TO-RT TRANSFER)

In non-burst mode, a DMA handshake will be initiated for each

data word received from the 1553 data bus. If successful, the

respective handshake will be followed by a corresponding write

cycle. A handshake timeout will not terminate transfer attempts for

the remaining data words, error flagging or Status Word transmis-

sion. After the reception of a valid non-mode code receive

Command Word followed by the correct number of valid Data

Words and assuming that all words are successfully transferred to

the subsystem, a negative pulse will be asserted on the Good

Block Received (GBR) output. The width of this pulse is two clock

cycles.

In burst mode, a DMA handshake will not be initiated until after all

data words have been received over the 1553 data bus and stored

into the SSRT's internal FIFO. After the handshake has been

negotiated, the SSRT will burst the contents of the FIFO to the

local bus (D0-D15). After the reception of a valid non-mode code

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61703G3-140Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61703G3-182K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61703G4-170Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F3-140S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F3-142L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61705 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Simple System RT |

| BU-61740B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61743 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61743F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。