- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166576 > BU-61703G4-200K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61703G4-200K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | CERAMIC, QFP-72 |

| 文件頁(yè)數(shù): | 41/54頁(yè) |

| 文件大?。?/td> | 576K |

| 代理商: | BU-61703G4-200K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

46

Data Device Corporation

www.ddc-web.com

BU-61703/61705

D1 web-09/02-0

DESCRIPTION

Remote Terminal Fail. This two-state output signal will be asserted low following a failure of the built-in self-test performed

following power turn-on or as the result of the receipt of an Initiate self-test mode command. The built-in off-line self-test

includes tests of the Manchester encoder and decoders, transmitter failsafe timer, and RT protocol logic.

In addition, RTFAIL will be asserted low following a failure of the on-line loop test for any non-broadcast message. The on-

line loop test verifies the validity of the received version of all transmitted words (sync, Manchester encoding, bit count,

parity), and includes a bit-by-bit comparison and verification of the last transmitted word.

If asserted to logic "0", RTFAIL will clear to logic "1" when the SSRT begins transmission of its status word in response to

a subsequent valid non-broadcast message.

Message Error. Active low level two-state output signal used to flag to the external system that there was a message

error on the 1553 bus communication (word, gap, or word count error) for a particular message. This output goes low

upon detecting the error and is reset following the receipt of the next valid command word (to the RT) from the 1553 bus,

or if MSTCLR is asserted low. If this output goes low, all further servicing of the current message is aborted.

Good Block Received. Low level two-state output pulse (2 clock cycles wide) that is used to indicate to the external sys-

tem that a valid, legal, non-mode receive command with the correct number of valid data words has been received and

transferred to the external system.

For non-burst mode, this pulse will occur after the last data word is transferred. Assuming a DTREQ-to-DTGRT time of 0,

this will be approximately 4 s following the mid-parity bit crossing of the last received data word.

For burst mode, the GBR pulse will begin synchronous with the rising edge of DTACK at the end of the burst write transfer.

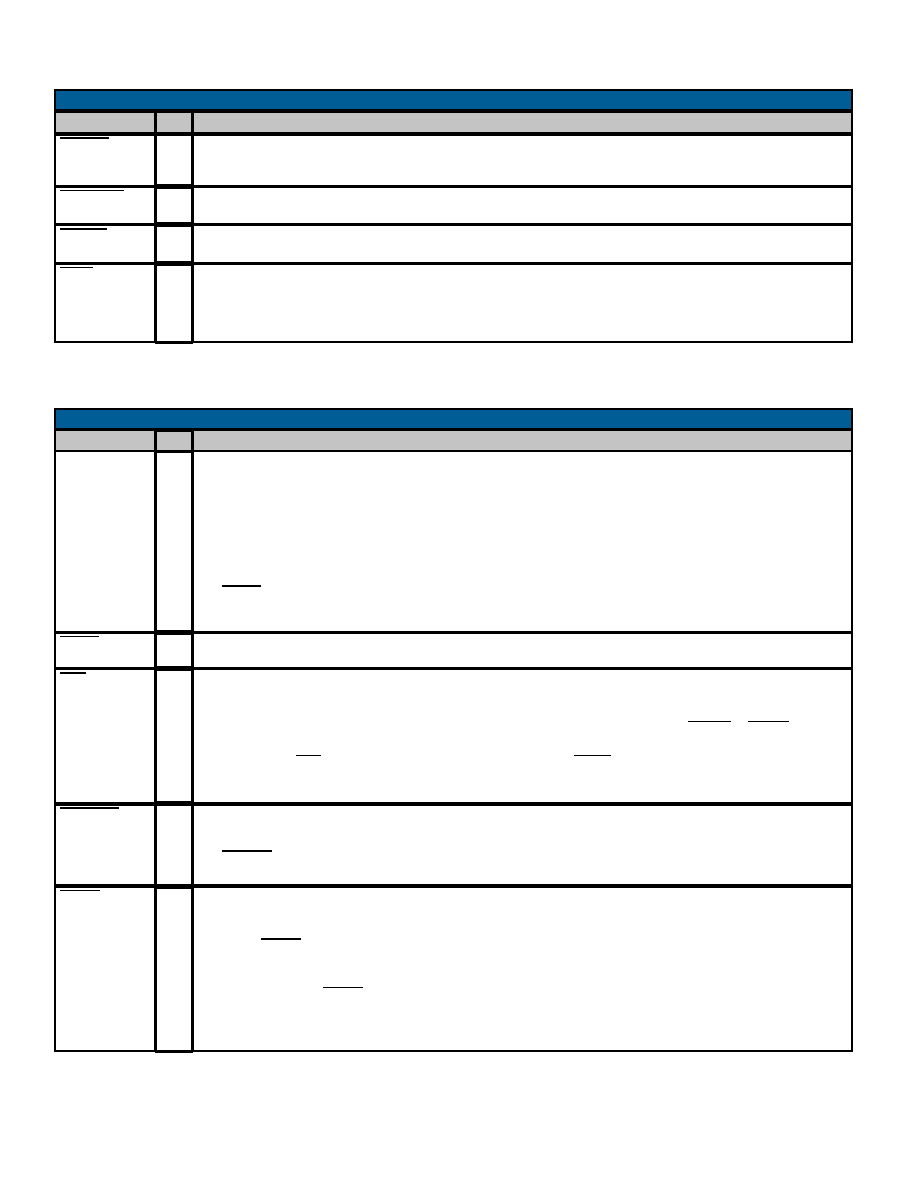

RTFAIL (O)

MSG_ERR (O)

GBR (O)

58

28

60

SIGNAL

TABLE 14. RT ACTIVITY AND MESSAGE STATUS INDICATORS

RT Active. This signal will be low (logic "0") following power turn-on, and when the SSRT is reading its Auto-configure

word or is performing its internal self-test. After the self-test passes, or if the Auto-configure option is not used, or if Auto-

configure is used but bit 5 of the Auto-configure word is logic "1" (meaning for the RT to always go online), RTACTIVE

will then transition to logic "1". When this occurs, the SSRT will begin processing messages over the 1553 bus.

If Auto-configure is enabled, and bit 5 of the Auto-configure word is logic "0" and the self-test fails, then RTACTIVE will

remain at logic "0". In this case, the SSRT will remain offline and not process any 1553 messages.

A failed self test will cause RTFAIL_L to be asserted low (logic “0").

If the auto-configure option is used, the external system should enable the configuration bits on D5-D0 when RTACTIVE

and DTACK are both outputting logic "0".

RTACTIVE

56

PIN

In-command. This two-state output is asserted low whenever a message is being processed by the SSRT.

INCMD

25

DESCRIPTION

Busy. If this input is asserted low, the Busy bit will be set to logic "1" in the SSRT's Status Word. If the Busy bit in the sta-

tus word is logic "1", the SSRT will not transmit any data words, except for a Transmit last command or Transmit BIT word

mode command. For a receive command, if the SSRT is Busy, it will still transfer data words to the external system

(although these transfers may be blocked by means of external logic).

Subsystem Flag. If this input is asserted low, the Subsystem Flag bit will be set in the SSRT's Status Word.

BUSY (I)

SSFLAG (I)

55

32

SIGNAL

TABLE 13. RT STATUS WORD INPUTS

Illegal. Input to the SSRT that is sampled after the Command Word transfer. A logic "0" will cause the Message Error bit in

the status response to be set (logic "1"), while a logic "1" on this input will have no effect on the Message Error bit.

ILLEGAL (I)

62

PIN

Service Request. When this input is logic "0", the Service request bit in the SSRT's status word will be logic "1". When

this input is logic "1", the Service request bit in the SSRT's status word will be logic "0".

SRV_RQST (I)

61

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61703G4-400Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F3-390Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F3-500S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F3-592 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705F4-420W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61705 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Simple System RT |

| BU-61740B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61743 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61743F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。