- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166576 > BU-61705G4-300W (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61705G4-300W |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | CERAMIC, QFP-72 |

| 文件頁(yè)數(shù): | 39/54頁(yè) |

| 文件大?。?/td> | 576K |

| 代理商: | BU-61705G4-300W |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)當(dāng)前第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

44

Data Device Corporation

www.ddc-web.com

BU-61703/61705

D1 web-09/02-0

3

L_BRO (O)

Latched Broadcast. This two-state output signal is latched following receipt of a new command word. For a broadcast

command, this signal outputs a value of logic "1". For a non-broadcast message, this signal will output logic "0".

4

T / R

Transmit/Receive. This two-state output signal is latched following receipt of a new command word. For a transmit mes-

sage, this signal will output a value of logic "1". For a receive message, this signal will output logic "0".

69

SA2 (O)

Subaddress. These five two-state output signals are latched following receipt of a new command word. They provide the

subaddress field of the received command word.

PIN

9

WC / MC /

CWC2 (O)

Word Count/Mode Code/Current Word Count. Following receipt of a new command word, these five two-state output sig-

nals provide the contents of the command word's Word Count/Mode Code field.

For a non-mode code receive message, the contents of WC/CWC are updated and incremented to reflect the value of the

current data word being transferred to the system (in non-burst mode), or to the internal FIFO (in burst mode). CWC

increments from 0 to the value of the Word Count field - 1 during the message.

At the end of a non-mode code receive message in burst mode, the contents of CWC will then increment from 0 to the

value of the word count field -1, as each word is transferred from the internal FIFO to the external system over D15-D0. In

burst mode, it takes three clock cycles to transfer each word to the external system.

For a non-mode code transmit command, the value of CWC starts from 0 and increments to the value of Word Count - 1,

as each word is read from the external system and transferred to the SSRT.

For a mode code command, the WC/CWC outputs the command word mode code field, which remains latched through

the end of the message (until receipt of a subsequent command word).

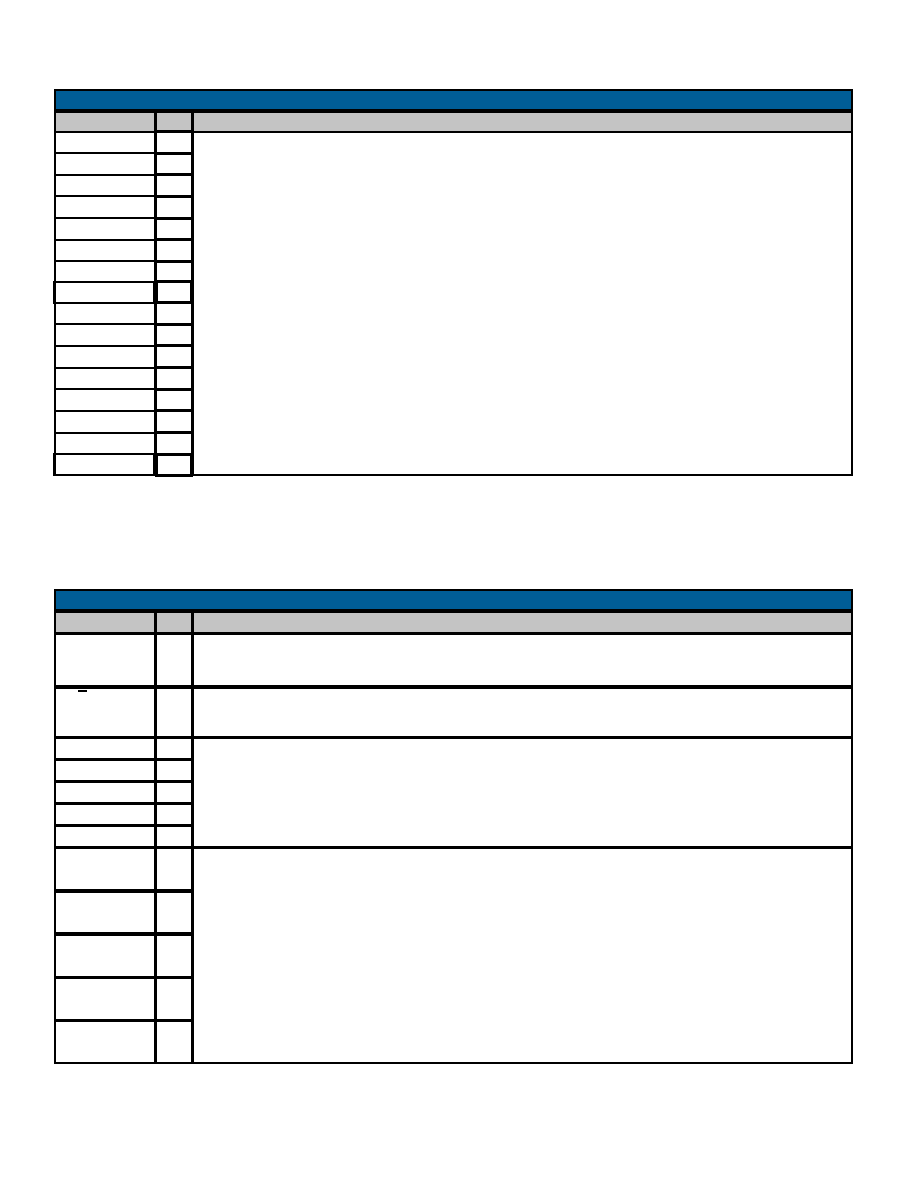

TABLE 10. COMMAND / ADDRESS BUS

SIGNAL

SA4 (O)

SA3 (O)

SA1 (O)

22

11

6

SA0 (O)

68

WC / MC /

CWC4 (O) (MSB)

WC / MC /

CWC3 (O)

WC / MC /

CWC1 (O)

27

12

DESCRIPTION

10

WC / MC /

CWC0 (O) (LSB)

15

Bi-directional data bus. When the SSRT is writing data to the external system, these signals are active outputs. At all

other times, these signals are high impedance inputs.

42

D10 (I/O)

D0 (I/O) (LSB)

38

D1 (I/O)

43

D2 (I/O)

44

D3 (I/O)

D4 (I/O)

39

45

D5 (I/O)

36

D6 (I/O)

47

D7 (I/O)

46

D8 (I/O)

51

54

D9 (I/O)

52

D11 (I/O)

49

D12 (I/O)

TABLE 9. DATA BUS (16)

48

D13 (I/O)

50

D14 (I/O)

53

D15 (I/O) (MSB)

DESCRIPTION

PIN

SIGNAL NAME

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61705G4-410L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705G4-490W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61703G3-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61703G3-420 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61705G4-120 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61740B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61743 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61743F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61743F4-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。