- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378432 > C513-1RN (SIEMENS A G) 8-Bit CMOS Microcontroller PDF資料下載

參數(shù)資料

| 型號: | C513-1RN |

| 廠商: | SIEMENS A G |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-Bit CMOS Microcontroller |

| 中文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| 文件頁數(shù): | 29/43頁 |

| 文件大小: | 692K |

| 代理商: | C513-1RN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

C511 / C513

Semiconductor Group

29

Power Saving Modes

Two power down modes are available, the idle mode and the power down mode. In the idle mode

only the CPU will be deactivated while in the power down mode the on-chip oscillator is stopped.

The bits PDE and IDLE select the power down mode or the idle mode, respectively. If the power

down mode and the idle mode are set at the same time, power down takes precedence.

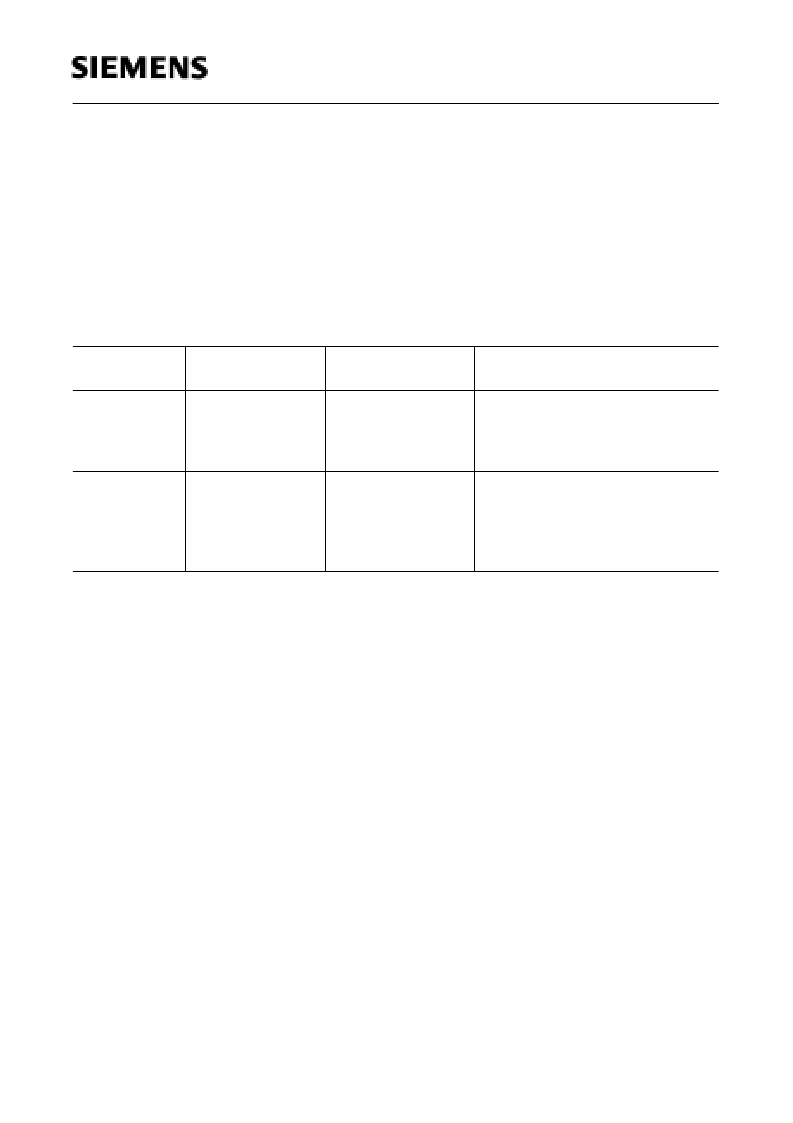

Table 15

gives a general overview of the power saving modes.

Table 15

Entering and leaving the power saving modes

In the power down mode of operation,

V

CC

can be reduced to minimize power consumption. It must

be ensured, however, that

V

CC

is not reduced before the power down mode is invoked, and that

V

CC

is restored to its normal operating level, before the power down mode is terminated. The reset signal

that terminates the power down mode also restarts the oscillator. The reset should not be activated

before

V

CC

is restored to its normal operating level and must be held active long enough to allow the

oscillator to restart and stabilize (similar to power-on reset).

Mode

Entering

Example

Leaving by

Remarks

Idle mode

ORL PCON, #01H

– enabled interrupt

– Hardware Reset

CPU is gated off

CPU status registers maintain

their data.

Peripherals are active

Power Down

Mode

ORL PCON, #02H

Hardware Reset

Oscillators are stopped. Contents

of on-chip RAM and SFR’s are

maintained

(leaving power down mode means

redefinition of SFR’s contents)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C513A-2RN | 8-Bit CMOS Microcontroller |

| C513A-LM | 8-Bit CMOS Microcontroller |

| C513A-LN | 8-Bit CMOS Microcontroller |

| C513A-RN | 8-Bit CMOS Microcontroller |

| C513AO | 8-bit CMOS Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| C5133 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| C5134 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| C-51343NFU-LY-AA | 制造商:OPTREX 功能描述: |

| C5134C2003 | 制造商:Glenair Inc 功能描述:CONNECTOR - Bulk |

| C5134C2005 | 制造商:Glenair Inc 功能描述:CONNECTOR - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。