- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223524 > CAT1232LPZ (ON SEMICONDUCTOR) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 PDF資料下載

參數(shù)資料

| 型號(hào): | CAT1232LPZ |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| 封裝: | GREEN, MSOP-8 |

| 文件頁數(shù): | 5/9頁 |

| 文件大小: | 179K |

| 代理商: | CAT1232LPZ |

5

CAT1232LP/CAT1832

Doc. No. 25089, Rev. B

2006 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

APPLICATION INFORMATION

SUPPLY VOLTAGE MONITOR

Reset Signal Polarity and Output Stage Structure

RESET is an active LOW signal. It is developed with an

open drain driver in the CAT1232LP. A pull-up resistor

is required, typical values are 10k

to 50k. The

CAT1832 uses a CMOS push-pull output stage for the

RESET.

RESET is an active High signal developed by a CMOS

push-pull output stage and is the logical opposite to

RESET.

Trip Point Tolerance Selection

The TOL input is used to select the VCC trip point

threshold. This selection is made connecting the TOL

input to ground or VCC. Connecting TOL to Ground

makes the VCC trip threshold 4.62V for the CAT1232LP

and 2.88V for the CAT1832.

Connecting TOL to VCC makes the VCC trip threshold

4.37V for the CAT1232LP and 2.55V for the CAT1832.

After VCC has risen above the trip point set by TOL,

RESET and

RESET remain active for a minimum time

period of 250ms.

On power-down, once VCC falls below the reset threshold

the RESET outputs will remain active and are guaranteed

valid down to a VCC level of 1.0V.

e

c

n

a

r

e

l

o

T

t

c

e

l

e

S

e

g

a

t

l

o

V

t

n

i

o

P

p

i

r

T

e

c

n

a

r

e

l

o

T

)

V

(

e

g

a

t

l

o

V

t

n

i

o

P

p

i

r

T

N

I

ML

A

N

I

M

O

NX

A

M

P

L

2

3

2

1

T

A

C

V

=

L

O

T

C

%

0

15

2

.

47

3

.

49

4

.

4

P

L

2

3

2

1

T

A

C

D

N

G

=

L

O

T

%

50

5

.

42

6

.

44

7

.

4

2

3

8

1

T

A

C

V

=

L

O

T

C

%

0

27

4

.

25

5

.

24

6

.

2

3

8

1

T

A

C

=

L

O

TD

N

G

%

0

10

8

.

28

8

.

27

9

.

2

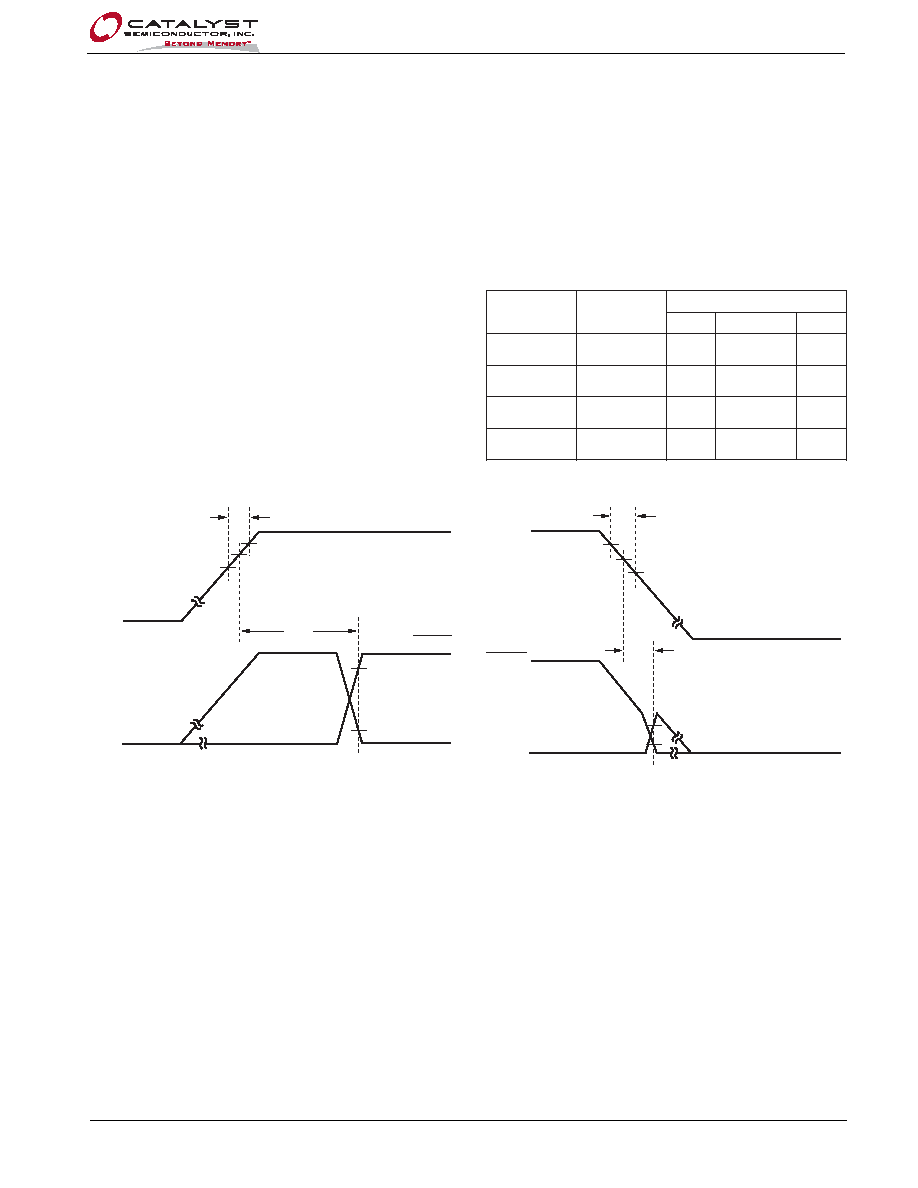

Figure 1. Timing Diagram: Power Up

Figure 2. Timing Diagram: Power Down

VCCTP(MAX)

VCCTP

VCCTP(MIN)

VCC

RESET

tR

tRPU

VOH

VOL

VCCTP(MAX)

VCCTP

VCCTP(MIN)

VCC

RESET

tF

VOH

VOL

tRPD

Manual Reset Operation

Push-button input,

PBRST, allows the user to issue

reset signals. The pushbutton input is debounced and is

pulled high through an internal 40k

resistor.

When

PBRST is held low for the minimum time of 20 ms,

both resets become active and remain active for a

minimum time period of 250ms after

PBRST returns

high.

No external pull-up resistor is required, since

PBRST is

pulled high by an internal 40k

resistor.

PBRST can be driven from a TTL or CMOS logic line or

short-ed to ground with a mechanical switch.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT1832R | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| CAT24C01BRA-1.8 | 128 X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 |

| CAT24C21PE | 128 X 8 I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| CAT24C642JA-42TE13 | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| CAT24C642PA-30 | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDIP8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT1232LPZ-G | 制造商:ON Semiconductor 功能描述:SUPERVISOR, 5 V - Rail/Tube |

| CAT1232LPZ-GT3 | 功能描述:監(jiān)控電路 SUP 5 V RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| CAT12787 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| CAT130019SWGI | 制造商:Catalyst Semiconductor 功能描述: |

| CAT130019SWI-G | 功能描述:監(jiān)控電路 2.93V, 1K EEPROM, Active Low RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。