- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366700 > CAT24WC64GWITE13D 32K/64K-Bit I2C Serial CMOS EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | CAT24WC64GWITE13D |

| 英文描述: | 32K/64K-Bit I2C Serial CMOS EEPROM |

| 中文描述: | 32K/64K-Bit I2C串行CMOS EEPROM的 |

| 文件頁(yè)數(shù): | 5/12頁(yè) |

| 文件大小: | 468K |

| 代理商: | CAT24WC64GWITE13D |

CAT24WC32/64

5

Doc. No. 1039, Rev. G

2005 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

I

2

C BUS PROTOCOL

The features of the I

2

C bus protocol are defined as

follows:

(1) Data transfer may be initiated only when the bus is

not busy.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any changes

in the data line while the clock line is high will be

interpreted as a START or STOP condition.

START Condition

The START Condition precedes all commands to the

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT24WC32/64 monitors

the SDA and SCL lines and will not respond until this

condition is met.

STOP Condition

A LOW to HIGH transition of SDA when SCL is HIGH

determines the STOP condition. All operations must end

with a STOP condition.

DEVICE ADDRESSING

The bus Master begins a transmission by sending a

START condition. The Master sends the address of the

particular slave device it is requesting. The four most

significant bits of the 8-bit slave address are fixed as

1010 (Fig. 5). The next three bits (A2, A1, A0) are the

device address bits; up to eight 32K/64K devices may

to be connected to the same bus. These bits must

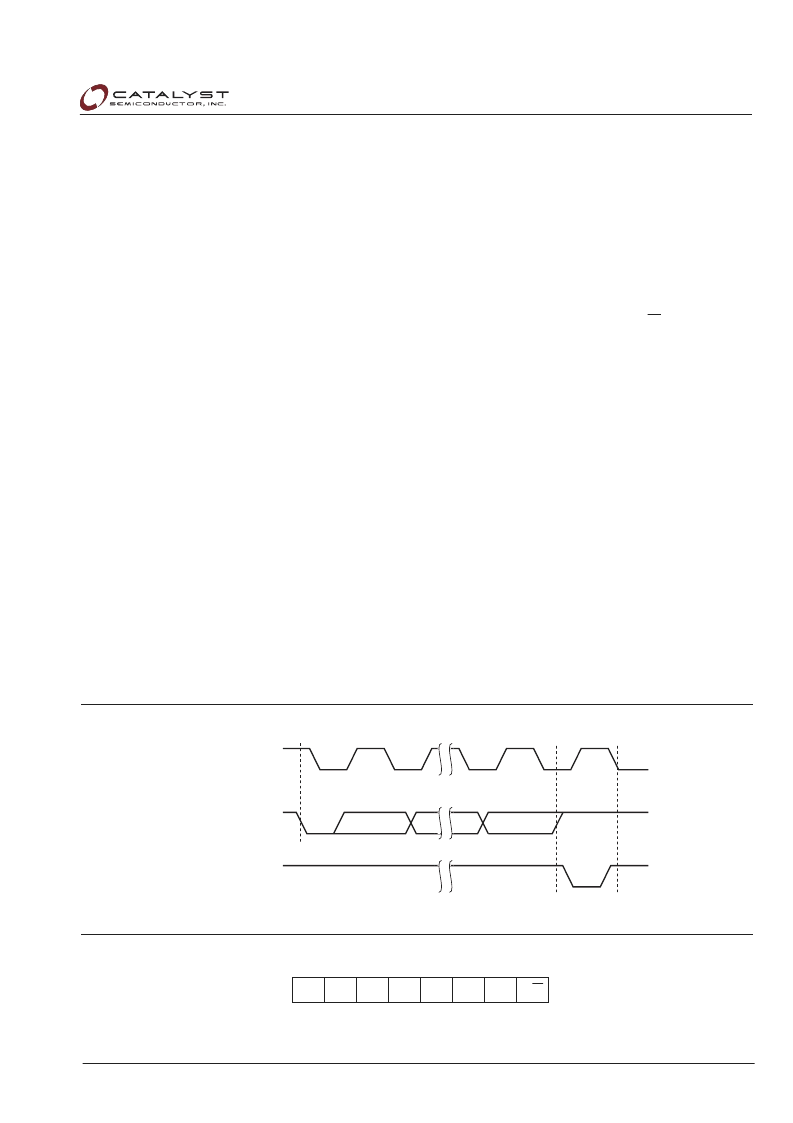

Figure 4. Acknowledge Timing

5027 FHD F07

Figure 5. Slave Address Bits

5020 FHD F06

ACKNOWLEDGE

1

START

SCL FROM

MASTER

8

9

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

1

0

1

0

A2

A1

A0

R/W

compare to the hardwired input pins, A2, A1 and A0. The

last bit of the slave address specifies whether a Read or

Write operation is to be performed. When this bit is set

to 1, a Read operation is selected, and when set to 0, a

Write operation is selected.

After the Master sends a START condition and the slave

address byte, the CAT24WC32/64 monitors the bus and

responds with an acknowledge (on the SDA line) when

its address matches the transmitted slave address. The

CAT24WC32/64 then performs a Read or Write opera-

tion depending on the state of the R/W bit.

Acknowledge

After a successful data transfer, each receiving device is

required to generate an acknowledge. The Acknowledg-

ing device pulls down the SDA line during the ninth clock

cycle, signaling that it received the 8 bits of data.

The CAT24WC32/64 responds with an acknowledge

after receiving a START condition and its slave address.

If the device has been selected along with a write

operation, it responds with an acknowledge after receiv-

ing each 8-bit byte.

When the CAT24WC32/64 begins a READ mode it

transmits 8 bits of data, releases the SDA line, and

monitors the line for an acknowledge. Once it receives

this acknowledge, the CAT24WC32/64 will continue to

transmit data. If no acknowledge is sent by the Master,

the device terminates data transmission and waits for a

STOP condition. The master must then issue a stop

condition to return the CAT24WC32/64 to the standby

power mode and place the device in a known state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT24WC64GWTE13B | 32K/64K-Bit I2C Serial CMOS EEPROM |

| CAT24WC64GWTE13D | 32K/64K-Bit I2C Serial CMOS EEPROM |

| CAT24WC64GX-1.8TE13B | 32K/64K-Bit I2C Serial CMOS EEPROM |

| CAT24WC64GX-1.8TE13D | 32K/64K-Bit I2C Serial CMOS EEPROM |

| CAT24WC64GXA-1.8TE13B | 32K/64K-Bit I2C Serial CMOS EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT24WC64J | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (8192x8) 64k RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT24WC64J-1.8 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (8192x8) 64k RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT24WC64JA | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (8192x8) 64k RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT24WC64JI | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (8192x8) 64k RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT24WC64JI-1.8 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 (8192x8) 64k RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。