- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366715 > CAT25C256P-1.8TE13 64K 8K x 8 Battery-Voltage CMOS E2PROM PDF資料下載

參數(shù)資料

| 型號: | CAT25C256P-1.8TE13 |

| 元件分類: | EEPROM |

| 英文描述: | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| 中文描述: | 64K的8K的× 8電池電壓的CMOS E2PROM的 |

| 文件頁數(shù): | 5/11頁 |

| 文件大?。?/td> | 79K |

| 代理商: | CAT25C256P-1.8TE13 |

5

CAT25C128/256

Doc. No. 25088-00 1/01

FUNCTIONAL DESCRIPTION

The CAT25C128/256 supports the SPI bus data trans-

mission protocol. The synchronous Serial Peripheral

Interface (SPI) helps the CAT25C128/256 to interface

directly with many of today’s popular microcontrollers.

The CAT25C128/256 contains an 8-bit instruction regis-

ter. (The instruction set and the operation codes are

detailed in the instruction set table)

After the device is selected with

CS

going low, the first

byte will be received. The part is accessed via the SI pin,

with data being clocked in on the rising edge of SCK.

The first byte contains one of the six op-codes that define

the operation to be performed.

PIN DESCRIPTION

SI: Serial Input

SI is the serial data input pin. This pin is used to input all

opcodes, byte addresses, and data to be written to the

25C128/256. Input data is latched on the rising edge of

the serial clock.

SO: Serial Output

SO is the serial data output pin. This pin is used to

transfer data out of the 25C128/256. During a read cycle,

data is shifted out on the falling edge of the serial clock.

SCK: Serial Clock

SCK is the serial clock pin. This pin is used to synchro-

nize the communication between the microcontroller

and the 25C128/256. Opcodes, byte addresses, or data

present on the SI pin are latched on the rising edge of the

SCK. Data on the SO pin is updated on the falling edge

of the SCK.

CS

: Chip Select

CS

is the Chip select pin.

CS

low enables the CAT25C128/

256 and

CS

high disables the CAT25C128/256.

CS

high

takes the SO output pin to high impedance and forces

the device into a Standby Mode (unless an internal write

operation is underway) The CAT25C128/256 draws

ZERO current in the Standby mode. A high to low

transition on

CS

is required prior to any sequence being

initiated. A low to high transition on

CS

after a valid write

sequence is what initiates an internal write cycle.

WP

: Write Protect

WP

is the Write Protect pin. The Write Protect pin will

allow normal read/write operations when held high.

When

WP

is tied low and the WPEN bit in the status

register is set to “1”, all write operations to the status

register are inhibited.

WP

going low while

CS

is still low

will interrupt a write to the status register. If the internal

write cycle has already been initiated,

WP

going low will

have no effect on any write operation to the status

register. The

WP

pin function is blocked when the WPEN

bit is set to 0.

HOLD

: Hold

HOLD

is the HOLD pin. The

HOLD

pin is used to pause

transmission to the CAT25C128/256 while in the middle

of a serial sequence without having to re-transmit entire

sequence at a later time. To pause,

HOLD

must be

brought low while SCK is low. The SO pin is in a high

impedance state during the time the part is paused, and

transitions on the SI pins will be ignored. To resume

communication,

HOLD

is brought high, while SCK is low.

(HOLD

should be held high any time this function is not

being used.)

HOLD

may be tied high directly to V

cc

or tied

to V

cc

through a resistor. Figure 9 illustrates hold timing

sequence.

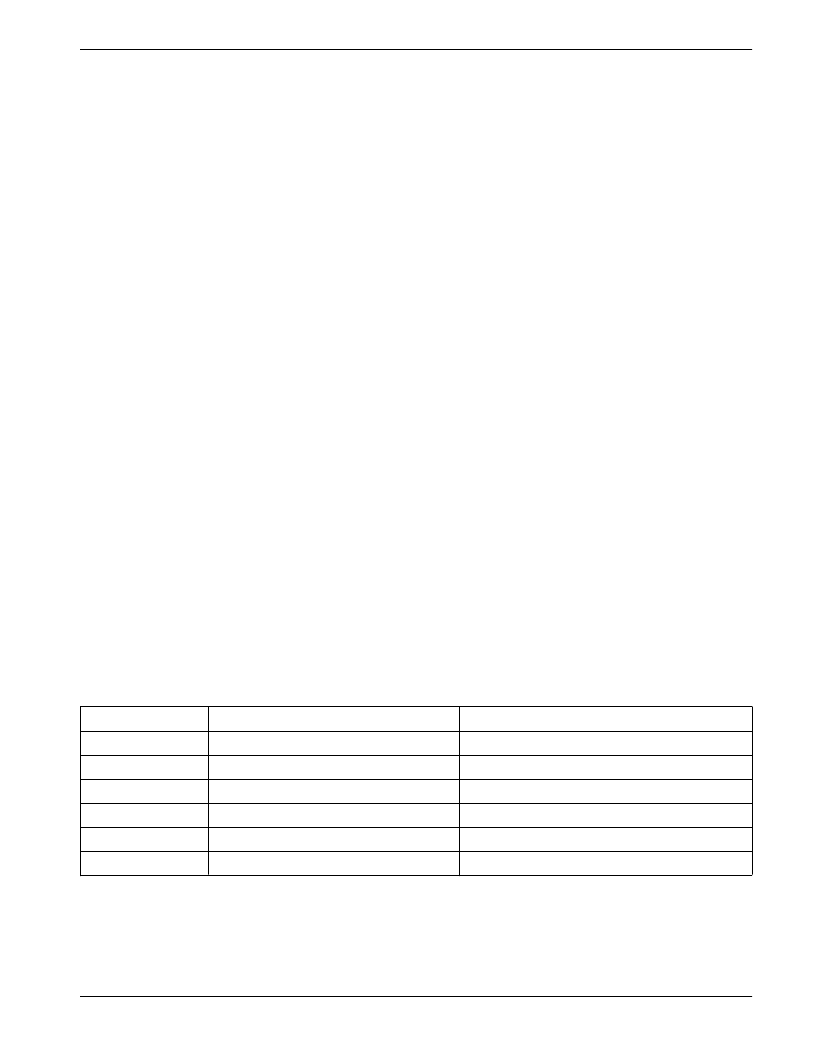

Instruction

Opcode

Operation

WREN

0000 0110

Enable Write Operations

WRDI

0000 0100

Disable Write Operations

RDSR

0000 0101

Read Status Register

WRSR

0000 0001

Write Status Register

READ

0000 0011

Read Data from Memory

WRITE

0000 0010

Write Data to Memory

INSTRUCTION SET

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT25C256PA-1.8TE13 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| CAT25C256PA-TE13 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| CAT25C256PI-1.8TE13 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| CAT25C256PI-TE13 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

| CAT25C256P-TE13 | 64K 8K x 8 Battery-Voltage CMOS E2PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT25C256PA | 功能描述:電可擦除可編程只讀存儲器 (32kx8) 256K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C256PI | 功能描述:電可擦除可編程只讀存儲器 (32kx8) 256K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C256PI-1.8 | 功能描述:電可擦除可編程只讀存儲器 (32kx8) 256K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C256X | 功能描述:電可擦除可編程只讀存儲器 (32kx8) 256K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C256X-1.8 | 功能描述:電可擦除可編程只讀存儲器 (32kx8) 256K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。