- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366768 > CAT93C56LI-T3 2-Kb Microwire Serial CMOS EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | CAT93C56LI-T3 |

| 英文描述: | 2-Kb Microwire Serial CMOS EEPROM |

| 中文描述: | 2 KB的Microwire串行EEPROM中的CMOS |

| 文件頁(yè)數(shù): | 4/18頁(yè) |

| 文件大小: | 370K |

| 代理商: | CAT93C56LI-T3 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

CAT93C56, CAT93C57

Doc. No. MD-1088 Rev. P

4

Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

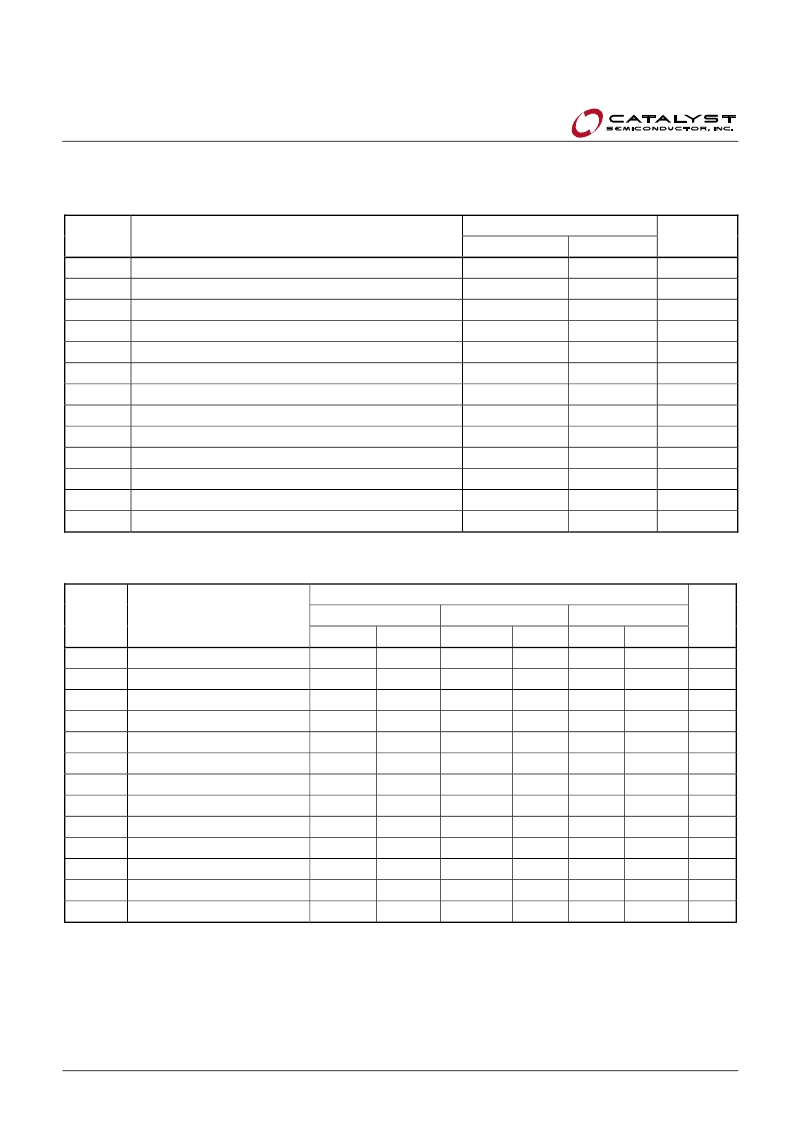

A.C. CHARACTERISTICS

(1)

, CAT93C56, Die Rev. G – New Product

V

CC

= +1.8V to +5.5V, T

A

= -40°C to +85°C, unless otherwise specified.

Limits

Symbol

Parameter

Min

50

0

100

100

0.25

0.25

0.25

DC

Max

0.25

0.25

100

5

0.25

2000

Units

t

CSS

t

CSH

t

DIS

t

DIH

t

PD1

t

PD0

t

HZ

t

EW

t

CSMIN

t

SKHI

t

SKLOW

t

SV

SK

MAX

CS Setup Time

CS Hold Time

DI Setup Time

DI Hold Time

Output Delay to 1

Output Delay to 0

Output Delay to High-Z

Program/Erase Pulse Width

Minimum CS Low Time

Minimum SK High Time

Minimum SK Low Time

Output Delay to Status Valid

Maximum Clock Frequency

ns

ns

ns

ns

μs

μs

ns

ms

μs

μs

μs

μs

kHz

(2)

A.C. CHARACTERISTICS

(1)

, CAT93C56/57, Die Rev. E – Mature Product

(CAT93C56 Rev. E - NOT RECOMMENDED FOR NEW DESIGNS)

Limits

V

CC

= 1.8V - 5.5V

Min

200

0

400

400

1

1

1

DC

V

CC

= 2.5V - 5.5V

Min

100

0

200

200

0.5

0.5

0.5

DC

V

CC

= 4.5V - 5.5V

Min

50

0

100

100

0.25

0.25

0.25

DC

Symbol

Parameter

Max

1

1

400

10

1

250

Max

0.5

0.5

200

10

0.5

500

Max

0.25

0.25

100

10

0.25

1000

Units

t

CSS

t

CSH

t

DIS

t

DIH

t

PD1

t

PD0

t

HZ

t

EW

t

CSMIN

t

SKHI

t

SKLOW

t

SV

SK

MAX

CS Setup Time

CS Hold Time

DI Setup Time

DI Hold Time

Output Delay to 1

Output Delay to 0

Output Delay to High-Z

Program/Erase Pulse Width

Minimum CS Low Time

Minimum SK High Time

Minimum SK Low Time

Output Delay to Status Valid

Maximum Clock Frequency

ns

ns

ns

ns

μs

μs

ns

ms

μs

μs

μs

μs

kHz

(2)

Notes

:

(1) Test conditions according to “A.C. Test Conditions” table.

(2) These parameters are tested initially and after a design or process change that affects the parameter according to appropriate

AEC-Q100 and JEDEC test methods.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT93C56VI-GT2 | 2-Kb Microwire Serial CMOS EEPROM |

| CAT93C56VI-GT3 | 2-Kb Microwire Serial CMOS EEPROM |

| CAT93C56VI-T2 | 2-Kb Microwire Serial CMOS EEPROM |

| CAT93C56VI-T3 | 2-Kb Microwire Serial CMOS EEPROM |

| CAT93C56VP2I-GT2 | 2-Kb Microwire Serial CMOS EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT93C56LIT3E | 制造商:CATALYST 制造商全稱(chēng):Catalyst Semiconductor 功能描述:2K-Bit Microwire Serial EEPROM |

| CAT93C56M | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:EEPROM |

| CAT93C56M1.8 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:EEPROM |

| CAT93C56M1.8TE13 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:EEPROM |

| CAT93C56MA | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:EEPROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。