- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378439 > CCU3000 (MICRONAS SEMICONDUCTOR HOLDING AG) Central Control Unit PDF資料下載

參數(shù)資料

| 型號: | CCU3000 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Central Control Unit |

| 中文描述: | MICROCONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 12/77頁 |

| 文件大小: | 837K |

| 代理商: | CCU3000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

CCU 3000, CCU 3000-I

CCU 3001, CCU 3001-I

MICRONAS INTERMETALL

12

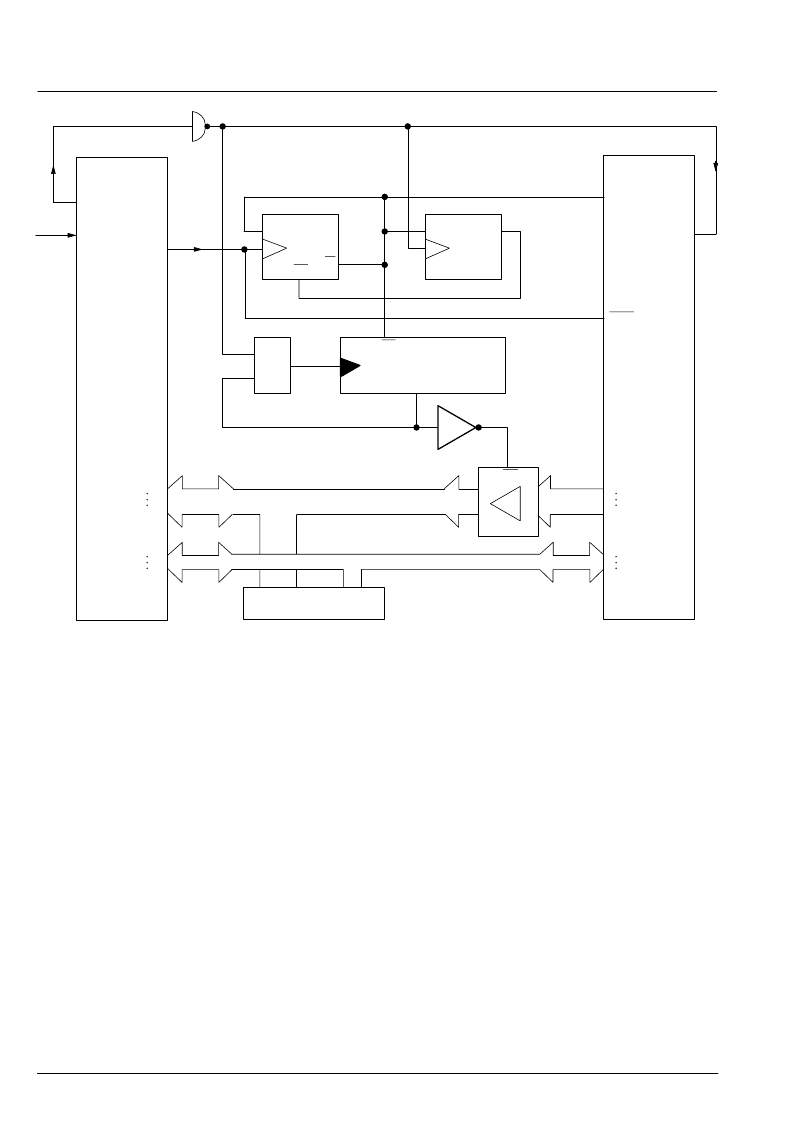

Fig. 2–12:

Using an external CPU

D

Q

A0...A15

ROM/RAM

D0...D7

D0

D7

A0

A15

XTAL1

XTAL2

CLK

in

Φ

Ext.

CPU

or

Emul.

RDY

IR

Counter

2

1

2 in

Q

clr

NMI

OR

clr

D

D0

D7

A0

A15

en

CCU

3000,

CCU

3001

EMU

Version

2.12. IM Bus Interface

The IM bus has been improved in its characteristics for

the CCU 3000, CCU 3001. In comparison to the inter-

face of the CCU 2000 series it differs in:

– multimaster ability

– 3 slave registers (8 bit wide)

– higher speed possible

The multimaster ability permits the use of several CCUs

on the same IM bus without impeding each other. Spe-

cially in add-on systems or systems with need of high

computing power and/or I/O requirements, this offers

great advantages. If several CCUs are admitted in a sys-

tem, it must be ascertained that these can communicate

with each other. A slave IM bus interface has been in-

stalled for this purpose. Parallel to the lines of the mas-

ter, three completely independent receiver registers

have been installed. All of these are constantly alert,

whether the master itself is active or not. As all CCUs

have the same IM bus addresses for these registers, the

contents of these registers (that is, for all CCUs that are

in the system) will be the same. The handshake

amongst these is realized in software, and one register

each is reserved for the device address, the request and

the data to be transported. The data rate can now be ad-

justed per software. It is possible to attain 1 MBit/s, if the

bus participants in question are devised to support this

rate. Also the actual realization of the bus can forbid

such a high data rate. The IM bus interface needs exter-

nal pull-up resistors.

In the I/O-page the IM bus interface reserves 8 bytes:

3 bytes

1 byte

2 bytes

1 byte

read:

slave receiving registers (read)

master address (write)

master data register (read/write)

control register (read/write)

bit 0 0... IM bus master ready

1... IM bus master busy

bit 1

1 Byte received in slave register 1

(may generate interrupt)

bit 2

IM-bus 1 control and status

(may generate interrupt)

bit 3 Word 3 Received (may generate

interrupt)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CCU3000-I | Central Control Unit |

| CCU3001 | Central Control Unit |

| CCU3001-I | Central Control Unit |

| CD-700-KAC-GAB-XX.XXX | Complete VCXO Based Phase Lock Loop |

| CD-700-LAF-GGB-XX.XXX | Complete VCXO Based Phase Lock Loop |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CCU3000I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CCU3000-I | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

| CCU3001 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

| CCU3001I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CCU3001-I | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。