- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378467 > CXA1854AR (Sony Corporation) Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C PDF資料下載

參數(shù)資料

| 型號(hào): | CXA1854AR |

| 廠商: | Sony Corporation |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C |

| 中文描述: | 電可擦除可編程邏輯器件 |

| 文件頁(yè)數(shù): | 24/45頁(yè) |

| 文件大小: | 1348K |

| 代理商: | CXA1854AR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

– 24 –

CXA1854AR

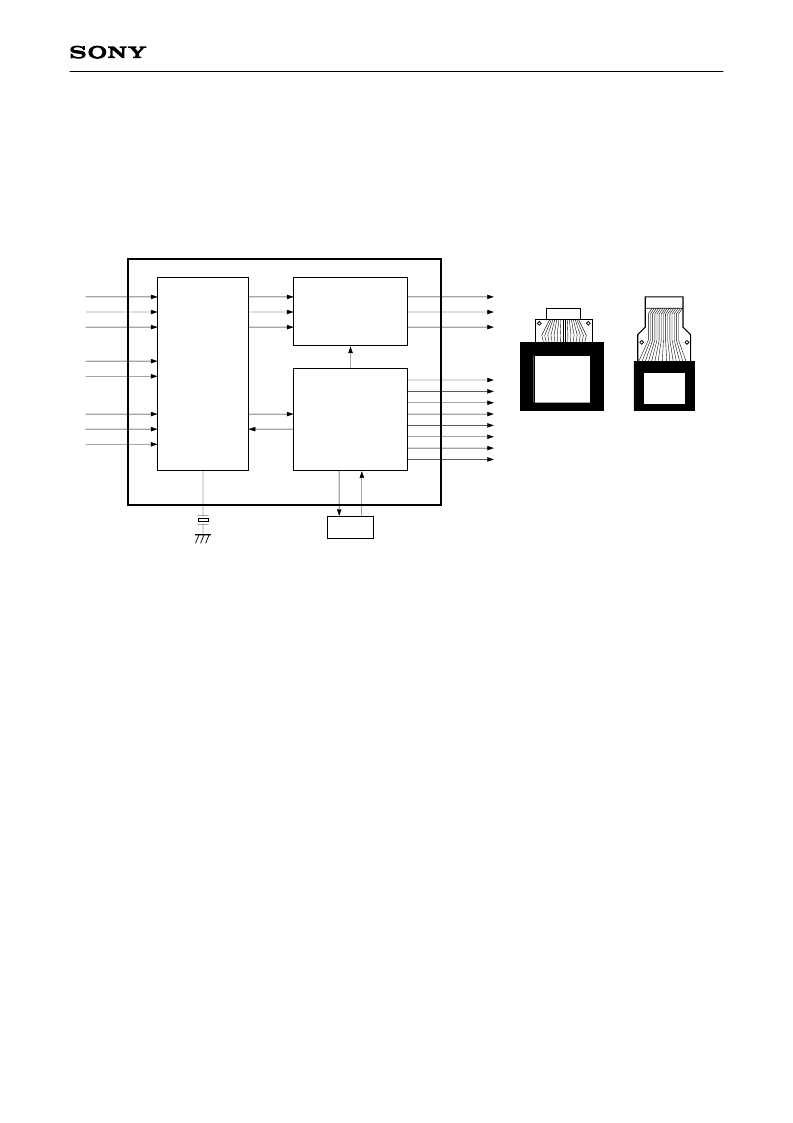

Description of Operation

The CXA1854AR incorporates the three functions of an RGB decoder block, an RGB driver block and a timing

generator (TG) block onto a single chip using BiCMOS technology. This section describes these functions and

their mutual relationship.

1) Description of the overall configuration

RGB decoder

EXT-R

EXT-G

EXT-B

Y

SYNC

C

R-Y

B-Y

CXA1854AR

ENB

CLR

VST1

VCK2

VCK1

HST1

HCK2

HCK1

FRP

R OUT

G OUT

B OUT

R

G

B

SYNC

BLK

3.58MHz

or 4.43MHz

R

C

RGB driver

TG

VCO

Corresponding LCD panels

LCX009AK/AKB

1.8cm 180K dots

LCX005BK/BKB

1.4cm 113K dots

2) Description of RGB decoder block operation

Input mode switching

Signal input: Composite input, Y/C input and Y/color difference input switching is supported by Pin 8

(MODE2).

During composite input:

The composite signal is input to Pins 1, 2 and 62.

During Y/C input:

The Y signal is input to Pins 1 and 2, and the C signal to Pin 62.

During Y/color difference input: The Y signal is input to Pins 1 and 2, the R-Y signal to Pin 50, and the B-Y

signal to Pin 49.

(Chroma signal input (delay line output) is also used during PAL, but is

switched with the MODE1 setting.)

Recommended input signal voltages for each mode are shown in the Pin Description table. The Y signal

enters the TRAP circuit in composite mode, but through operation is performed in all other modes. Also, the

picture center frequency is set separately for composite input and Y/C input. (See the AC Characteristics

tables.)

NTSC/PAL switching

NTSC and PAL (DPAL using an external delay line and SPAL) are switched by MODE1.

The built-in TRAP and BPF center frequencies are switched automatically according to the external crystal.

The center frequency is stabilized by the APC operation.

The R-Y demodulation detective axis is set internally to 90° during SPAL/DPAL. However, optimally adjust

the demodulation phase axis with the HUE adjustment pin.

Video AGC/ACC circuit

Different AGC characteristics are obtained depending on the APL level of the luminance signal. The gain for

the luminance signal is adjusted with the average value. The sync amplitude of the burst signal output is

detected and used to adjust the ACC amplifier gain.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CXA1855Q | Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C |

| CXA1855S | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

| CXA1866Q | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

| CXA1870 | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

| CXA1870S | Single Supply RS232C Line Driver/Receiver(?????μ?o?RS232C ?o?????????¨???2???2??????) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CXA1875AM | 制造商:Panasonic Industrial Company 功能描述:IC |

| CXA1998AQT6 | 制造商:Panasonic Industrial Company 功能描述:IC |

| CXA1998QT6 | 制造商:Panasonic Industrial Company 功能描述:IC |

| CXA20 | 制造商:ARTESYN 制造商全稱:Artesyn Technologies 功能描述:20W DC/DC Converters |

| CXA2000 | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:Y/C/RGB/D for PAL/NTSC Color TVs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。