- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378481 > CY23S05 (Cypress Semiconductor Corp.) Low-Cost 3.3V Spread Aware Zero Delay Buffer(低價(jià)格3.3V Spread Aware零延遲緩沖器) PDF資料下載

參數(shù)資料

| 型號(hào): | CY23S05 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | Low-Cost 3.3V Spread Aware Zero Delay Buffer(低價(jià)格3.3V Spread Aware零延遲緩沖器) |

| 中文描述: | 低成本3.3V的價(jià)差意識(shí)到零延遲緩沖器(低價(jià)格3.3蔓延意識(shí)到零延遲緩沖器) |

| 文件頁(yè)數(shù): | 2/9頁(yè) |

| 文件大?。?/td> | 207K |

| 代理商: | CY23S05 |

CY23S09

CY23S05

Document #: 38-07296 Rev. *C

Page 2 of 9

Zero Delay and Skew Control

All outputs should be uniformly loaded to achieve Zero Delay

between the input and output. Since the CLKOUT pin is the

internal feedback to the PLL, its relative loading can adjust the

input-output delay. This is shown in the above graph.

For applications requiring zero input-output delay, all outputs,

including CLKOUT, must be equally loaded. Even if CLKOUT

is not used, it must have a capacitive load equal to that on

other outputs, for obtaining zero input-output delay. If input to

output delay adjustments are required, use the above graph to

calculate loading differences between the CLKOUT pin and

other outputs.

For zero output-output skew, be sure to load all outputs

equally. For further information, refer to the application note

“CY23S05 and CY23S09 as PCI and SDRAM Buffers.”

Spread Aware

Many systems being designed now utilize a technology called

Spread Spectrum Frequency Timing Generation. Cypress has

been one of the pioneers of SSFTG development, and we

designed this product so as not to filter off the Spread

Spectrum feature of the Reference input, assuming it exists.

When a zero delay buffer is not designed to pass the SS

feature through, the result is a significant amount of tracking

skew which may cause problems in systems requiring

synchronization.

For more details on Spread Spectrum timing technology,

please see the Cypress application note entitled, “EMI

Suppression Techniques with Spread Spectrum Frequency

Timing Generator (SSFTG) ICs.”

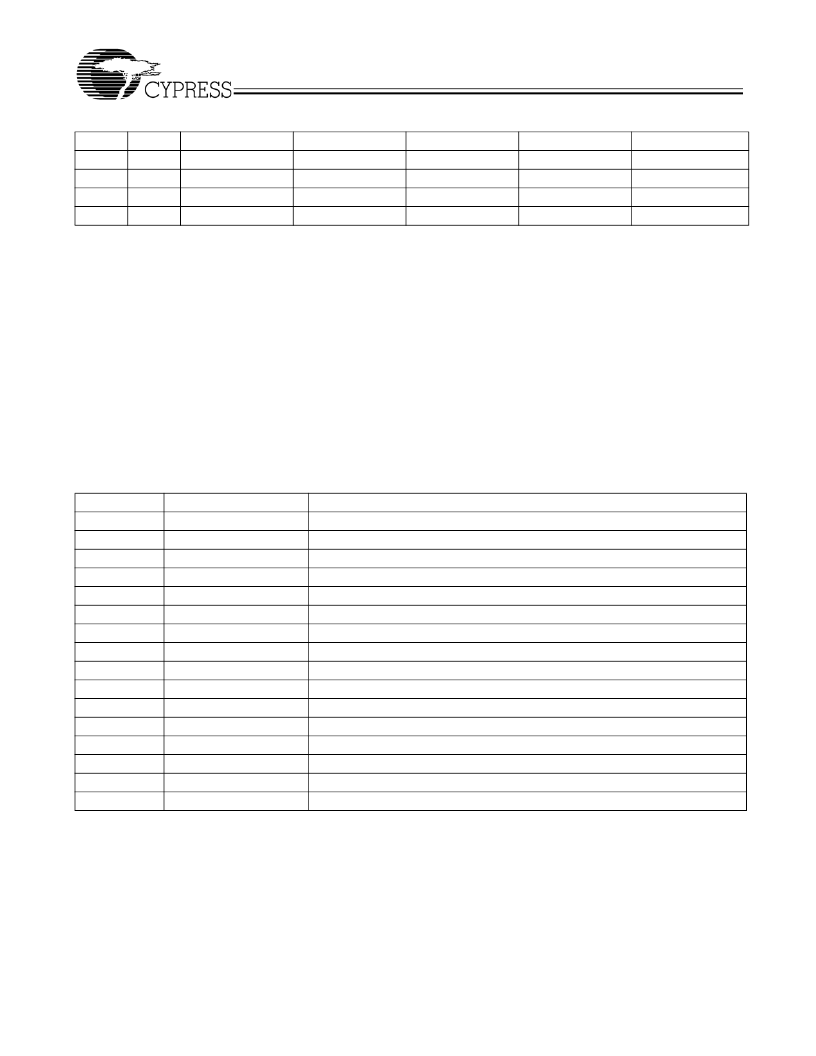

Select Input Decoding for CY23S09

S2

0

0

1

1

S1

0

1

0

1

CLOCK A1–A4

Three-state

Driven

Driven

Driven

CLOCK B1–B4

Three-state

Three-state

Driven

Driven

CLKOUT

[1]

Driven

Driven

Driven

Driven

Output Source

PLL

PLL

Reference

PLL

PLL Shut-down

N

N

Y

N

Pin Description for CY23S09

Pin

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Signal

Description

REF

[2]

CLKA1

[3]

CLKA2

[3]

V

DD

GND

CLKB1

[3]

CLKB2

[3]

S2

[4]

S1

[4]

CLKB3

[3]

CLKB4

[3]

GND

V

DD

CLKA3

[3]

CLKA4

[3]

CLKOUT

[3]

Input reference frequency, 5V-tolerant input

Buffered clock output, bank A

Buffered clock output, bank A

3.3V supply

Ground

Buffered clock output, bank B

Buffered clock output, bank B

Select input, bit 2

Select input, bit 1

Buffered clock output, bank B

Buffered clock output, bank B

Ground

3.3V supply

Buffered clock output, bank A

Buffered clock output, bank A

Buffered output, internal feedback on this pin

Notes:

1. This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the reference and output.

2. Weak pull-down.

3. Weak pull-down on all outputs.

4. Weak pull-up on these inputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY23S09 | Low-Cost 3.3V Spread Aware Zero Delay Buffer(低價(jià)格3.3V Spread Aware零延遲緩沖器) |

| CY24130-1 | HOTLink SMPTE Receiver Training Clock |

| CY24130 | HOTLink SMPTE Receiver Training Clock |

| CY24130-2 | HOTLink SMPTE Receiver Training Clock |

| CY24130ZXC-1 | Coaxial Cable; Impedance:75ohm; Conductor Size AWG:30; No. Strands x Strand Size:7 x 38; Jacket Material:Polyvinylchloride (PVC); Leaded Process Compatible:Yes RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY23S05SC-1 | 制造商:Cypress Semiconductor 功能描述: |

| CY23S05SC-1H | 制造商:Cypress Semiconductor 功能描述: 制造商:Rochester Electronics LLC 功能描述:ZERO DELAY BUFFER 3.3 V SPREAD AWARE - Bulk |

| CY23S05SC-1T | 功能描述:鎖相環(huán) - PLL Zero Delay Buffr COM RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY23S05SI-1 | 功能描述:鎖相環(huán) - PLL Zero Delay Buffr IND RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY23S05SI-1T | 功能描述:鎖相環(huán) - PLL Zero Delay Buffer Spread Aware RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。