- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379026 > CY37128P100-167AC (CYPRESS SEMICONDUCTOR CORP) 5V, 3.3V, ISR⑩ High-Performance CPLDs PDF資料下載

參數(shù)資料

| 型號: | CY37128P100-167AC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 5V, 3.3V, ISR⑩ High-Performance CPLDs |

| 中文描述: | EE PLD, 6.5 ns, PQFP100 |

| 封裝: | PLASTIC, TQFP-100 |

| 文件頁數(shù): | 7/62頁 |

| 文件大?。?/td> | 1782K |

| 代理商: | CY37128P100-167AC |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

Ultra37000 CPLD Family

Document #: 38-03007 Rev. *C

Page 7 of 62

Clocking

Each I/O and buried macrocell has access to four synchronous

clocks (CLK0, CLK1, CLK2 and CLK3) as well as an

asynchronous product term clock PTCLK. Each input

macrocell has access to all four synchronous clocks.

Dedicated Inputs/Clocks

Five pins on each member of the Ultra37000 family are desig-

nated as input-only. There are two types of dedicated inputs

on Ultra37000 devices: input pins and input/clock pins.

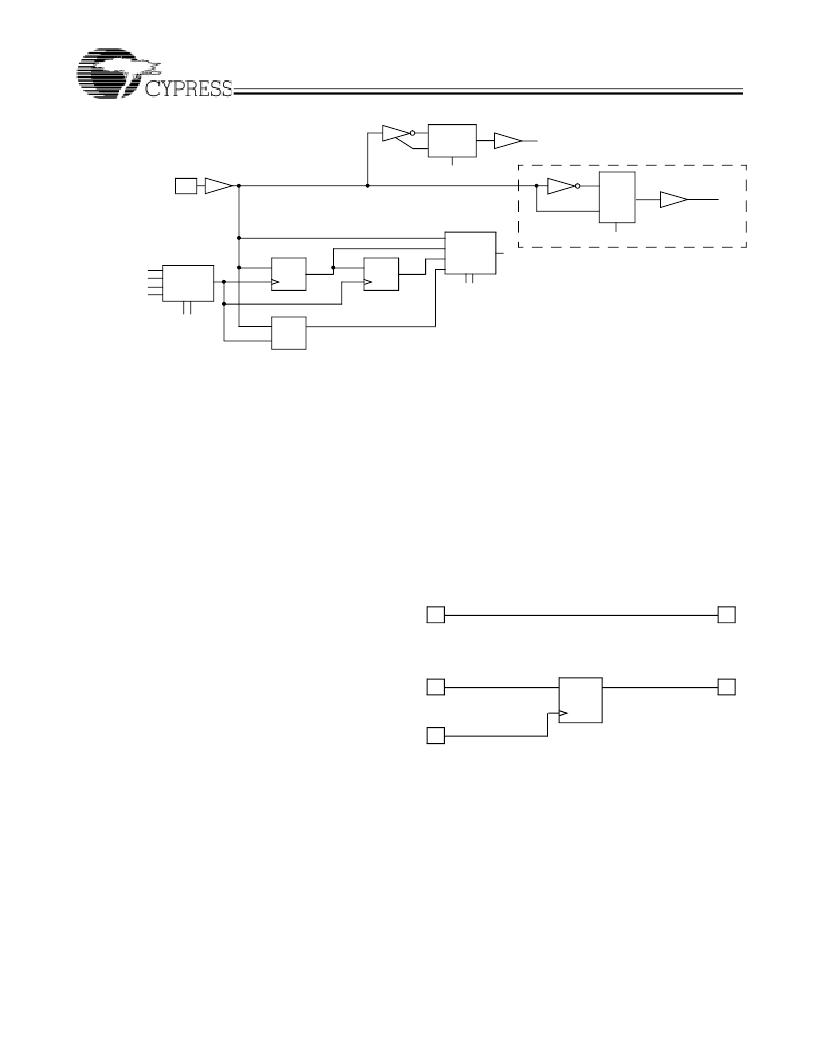

Figure 3

illustrates the architecture for input pins. Four input

options are available for the user: combinatorial, registered,

double-registered, or latched. If a registered or latched option

is selected, any one of the input clocks can be selected for

control.

Figure 4

illustrates the architecture for the input/clock pins.

Like the input pins, input/clock pins can be combinatorial,

registered, double-registered, or latched. In addition, these

pins feed the clocking structures throughout the device. The

clock path at the input has user-configurable polarity.

Product Term Clocking

In addition to the four synchronous clocks, the Ultra37000

family also has a product term clock for asynchronous

clocking. Each logic block has an independent product term

clock which is available to all 16 macrocells. Each product term

clock also supports user configurable polarity selection.

Timing Model

One of the most important features of the Ultra37000 family is

the simplicity of its timing. All delays are worst case and

system performance is unaffected by the features used.

Figure

5

illustrates the true timing model for the 167-MHz devices in

high speed mode. For combinatorial paths, any input to any

output incurs a 6.5-ns worst-case delay regardless of the

amount of logic used. For synchronous systems, the input set-

up time to the output macrocells for any input is 3.5 ns and the

clock to output time is also 4.0 ns. These measurements are

for any output and synchronous clock, regardless of the logic

used.

The Ultra37000 features:

No fanout delays

No expander delays

No dedicated vs. I/O pin delays

No additional delay through PIM

No penalty for using 0–16 product terms

No added delay for steering product terms

No added delay for sharing product terms

No routing delays

No output bypass delays

The simple timing model of the Ultra37000 family eliminates

unexpected performance penalties.

JTAG and PCI Standards

PCI Compliance

5V operation of the Ultra37000 is fully compliant with the PCI

Local Bus Specification published by the PCI Special Interest

Group. The 3.3V products meet all PCI requirements except

for the output 3.3V clamp, which is in direct conflict with 5V

tolerance. The Ultra37000 family’s simple and predictable

timing model ensures compliance with the PCI AC specifica-

tions independent of the design.

Figure 4. Input/Clock Macrocell

0

1

2

3

O

C10C11

TO PIM

D

Q

D

Q

D

Q

LE

INPUT/CLOCK PIN

0

1

2

3

O

FROM CLOCK

POLARITY INPUT

CLOCK PINS

0

1

O

C12

TO CLOCK MUX ON

ALL INPUT MACROCELLS

TO CLOCK MUX

IN EACH

0

1

CLOCK POLARITY MUX

ONE PER LOGIC BLOCK

FOR EACH CLOCK INPUT

C8 C9

C13, C14, C15

OR C16

O

Figure 5. Timing Model for CY37128

COMBINATORIAL SIGNAL

REGISTERED SIGNAL

D,T,L

O

CLOCK

INPUT

INPUT

OUTPUT

OUTPUT

t

S

= 3.5 ns

t

CO

= 4.5 ns

t

PD

= 6.5 ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY37128P100-167AXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37128VP256-143BGXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY3732VP84-83BBXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY3732VP84-83BGXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY3732VP84-83JXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY37128P100-167AXC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37128P160-100AC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY37128P160-100AI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37128P160-100AXC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 128 Macrocell 5V COM RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| CY37128P160-125AC | 功能描述:IC CPLD 128 MACROCELL 160LQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:Ultra37000™ 標(biāo)準(zhǔn)包裝:40 系列:ispMACH® 4000C 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時間 tpd(1):5.0ns 電壓電源 - 內(nèi)部:1.65 V ~ 1.95 V 邏輯元件/邏輯塊數(shù)目:32 宏單元數(shù):512 門數(shù):- 輸入/輸出數(shù):128 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:176-LQFP 供應(yīng)商設(shè)備封裝:176-TQFP(24x24) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。