- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170345 > CY38030V256-66BBC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 18.9 ns, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | CY38030V256-66BBC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, 18.9 ns, PBGA256 |

| 封裝: | 17 X 17 MM, 1.60 MM HEIGHT, TFBGA-256 |

| 文件頁(yè)數(shù): | 31/32頁(yè) |

| 文件大?。?/td> | 929K |

| 代理商: | CY38030V256-66BBC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 8 of 32

Channel Memory Routing Interface

Similar to LBC outputs, the channel memory blocks feature

dedicated tracks in the horizontal and vertical routing channels

for the data outputs and the flag outputs, as shown in Figure

5. This allows the channel memory blocks to be expanded

easily. These dedicated lines can be routed to I/O pins as chip

outputs or to other logic block clusters to be used in logic equa-

tions.

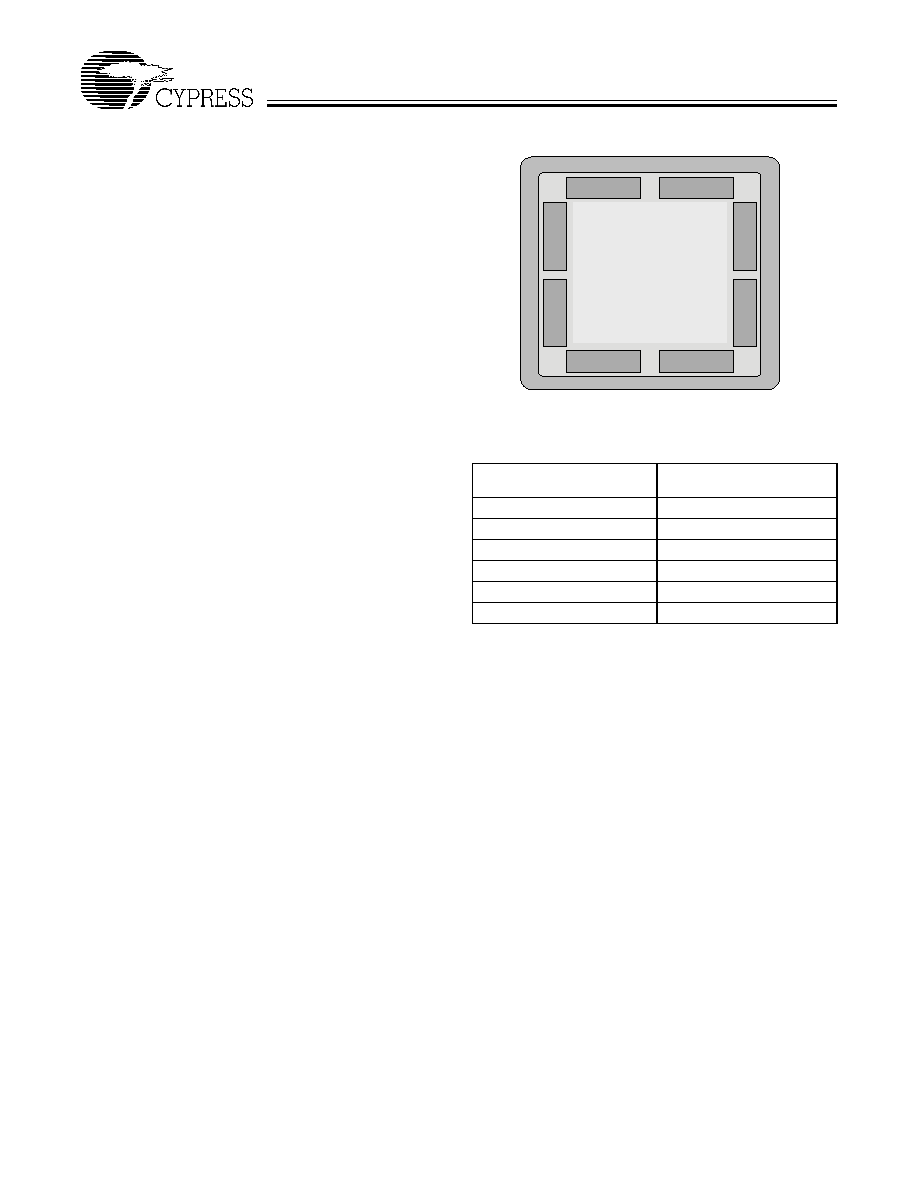

I/O Banks

The Quantum38K interfaces the horizontal and vertical routing

channels to the pins through I/O banks. There are 8 I/O banks

per device as shown in Figure 6, and all I/Os from an I/O bank

are located in the same section of a package for PCB layout

convenience.

For each package type, Quantum38K devices of different den-

sities keep given pins in the same I/O banks. This supports

and simplifies design migration across densities.

Each I/O bank contains several I/O cells, and each I/O cell

contains an input/output register, an output enable register,

programmable slew rate control and programmable bus hold

control logic. Each I/O cell drives a pin output of the device;

the cell also supplies an input to the device that connects to a

dedicated track in the associated routing channel.

There are four dedicated inputs (GCTL[3:0]) that are used as

Global Control Signals available to every I/O cell. These global

control signals may be used as output enables, register resets

and register clock enables as shown in Figure 7.

Each I/O bank can use any supported I/O standard by supply-

ing appropriate VCCIO voltages. All the VCCIO pins in an I/O

bank must be connected to the same VCCIO voltage. This re-

quirement restricts the number of I/O standards supported by

an I/O bank at any given time.

Figure 6. Quantum38K I/O Bank Block Diagram

.

IO Standards

I/O

Standard

VCCIO

LVTTL

3.3V

LVCMOS

3.3V

LVCMOS3

3.0V

LVCMOS2

2.5V

LVCMOS18

1.8V

3.3V PCI

3.3V

Delta39K

bank

0

bank

1

bank

4

bank

5

bank 2

bank 3

bank 6

bank 7

Quantum38K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY38030V256-66BBI | LOADABLE PLD, 18.9 ns, PBGA256 |

| CY38050V208-83NC | LOADABLE PLD, 15 ns, PQFP208 |

| CY38050V256-83BBC | LOADABLE PLD, 15 ns, PBGA256 |

| CY38050V484-83BBC | LOADABLE PLD, 15 ns, PBGA484 |

| CY38050V208-125NC | LOADABLE PLD, 10 ns, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。