- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170345 > CY39030Z144-83BBI (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 15 ns, PBGA144 PDF資料下載

參數(shù)資料

| 型號(hào): | CY39030Z144-83BBI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, 15 ns, PBGA144 |

| 封裝: | 1 MM PITCH, FBGA-144 |

| 文件頁數(shù): | 12/57頁 |

| 文件大小: | 1166K |

| 代理商: | CY39030Z144-83BBI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

PRELIMINARY

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. **

Page 2 of 57

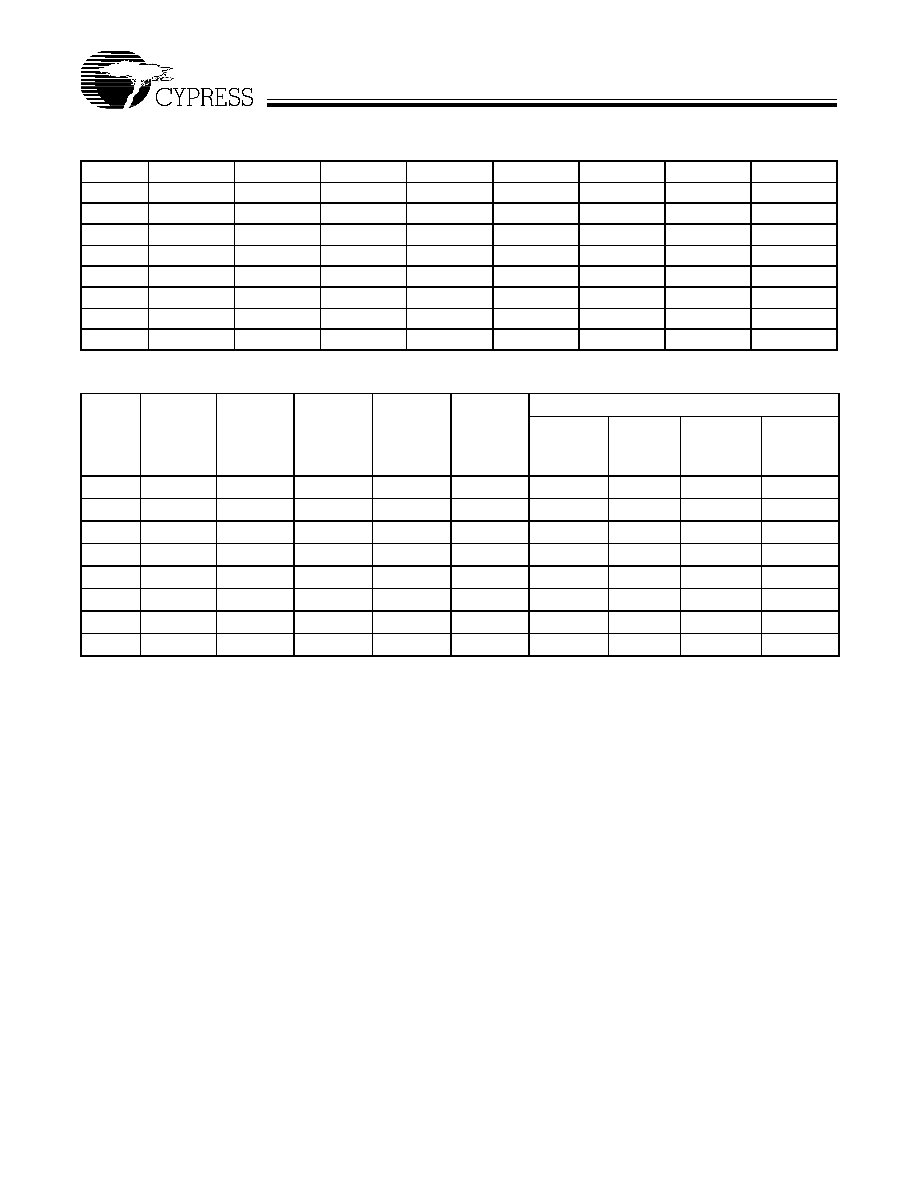

Delta39K Speed Bins[3]

Device

250

222

200

181

167

154

125

83

39K15

X

XX

39K30

X

39K50

X

39K100

X

39K165

X

39K200

X

39K250

X

39K350

XXX

Device Package Offering and I/O Count Including Dedicated Clock and Control Inputs

Device

208-EQFP

28X28 mm

0.5-mm

pitch

144-FBGA

13x13 mm

1.0-mm

pitch

256-FBGA

17x17 mm

1.0-mm

pitch

484-FBGA

23x23 mm

1.0-mm

pitch

676-FBGA

27x27 mm

1.0-mm

pitch

Self-Boot Solution[4]

256-FBGA

17x17 mm

1.0-mm

pitch

388-BGA

35x35 mm

1.27-mm

pitch

484-FBGA

23x23 mm

1.0-mm pitch

676-FBGA

27x27 mm

1.0-mm

pitch

39K15

134

92

134

39K30

136

92

176

39K50

136

180

218

39K100

136

180

302

294

302

39K165

136

356

294

386

39K200

136

368

294

428

39K250

136

470

294

470

39K350

136

520

294

520

Notes:

3.

Speed bins shown here are for Commercial operating range. Please refer to Delta39K Ordering Information on page 41 for Industrial range speed bins.

4.

Self-Boot Solution integrates the boot PROM (Flash Memory) with Delta39K die inside the same package.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY39030Z208-222NC | LOADABLE PLD, 7 ns, PQFP208 |

| CY39030Z256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

| CY39030Z256-222MBC | LOADABLE PLD, 7 ns, PBGA256 |

| CY39050V208-222NTC | LOADABLE PLD, 7 ns, PQFP208 |

| CY39050V256-222BBC | LOADABLE PLD, 7 ns, PBGA256 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY39030Z208-125BBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39030Z208-125BBI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39030Z208-125BGC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39030Z208-125BGI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39030Z208-125MBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。