- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379056 > CY7C1061AV33-10ZXI (CYPRESS SEMICONDUCTOR CORP) 16-Mbit (1M x 16) Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1061AV33-10ZXI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 16-Mbit (1M x 16) Static RAM |

| 中文描述: | 1M X 16 STANDARD SRAM, 10 ns, PDSO54 |

| 封裝: | 22.40 X 11.84 MM, 1 MM HEIGHT, LEAD FREE, TSOP2-54 |

| 文件頁(yè)數(shù): | 4/10頁(yè) |

| 文件大小: | 566K |

| 代理商: | CY7C1061AV33-10ZXI |

CY7C1061AV33

Document #: 38-05256 Rev. *G

Page 4 of 10

Notes

6. Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified

I

/I

and specified transmission line loads. Test conditions for the Read cycle use output loading shown in (a) of the

“AC Test Loads and Waveforms

” on

page 3

, unless specified otherwise.

7. This part has a voltage regulator that steps down the voltage from 3V to 2V internally. t

time must be provided initially before a Read/Write operation is started.

8. t

, t

, t

, t

HZBE

and t

, t

, t

, t

are specified with a load capacitance of 5 pF as in (b) of

“AC Test Loads and Waveforms

” on page 3

.

Transition is measured

200 mV from steady-state voltage.

9. These parameters are guaranteed by design and are not tested.

10.The internal Write time of the memory is defined by the overlap of CE

LOW (CE

HIGH) and WE LOW. Chip enables must be active and WE and byte enables

must be LOW to initiate a Write, and the transition of any of these signals can terminate the Write. The input data setup and hold timing should be referenced to

the leading edge of the signal that terminates the Write.

11. The minimum Write cycle time for Write Cycle No. 2 (WE controlled, OE LOW) is the sum of t

HZWE

and t

SD

.

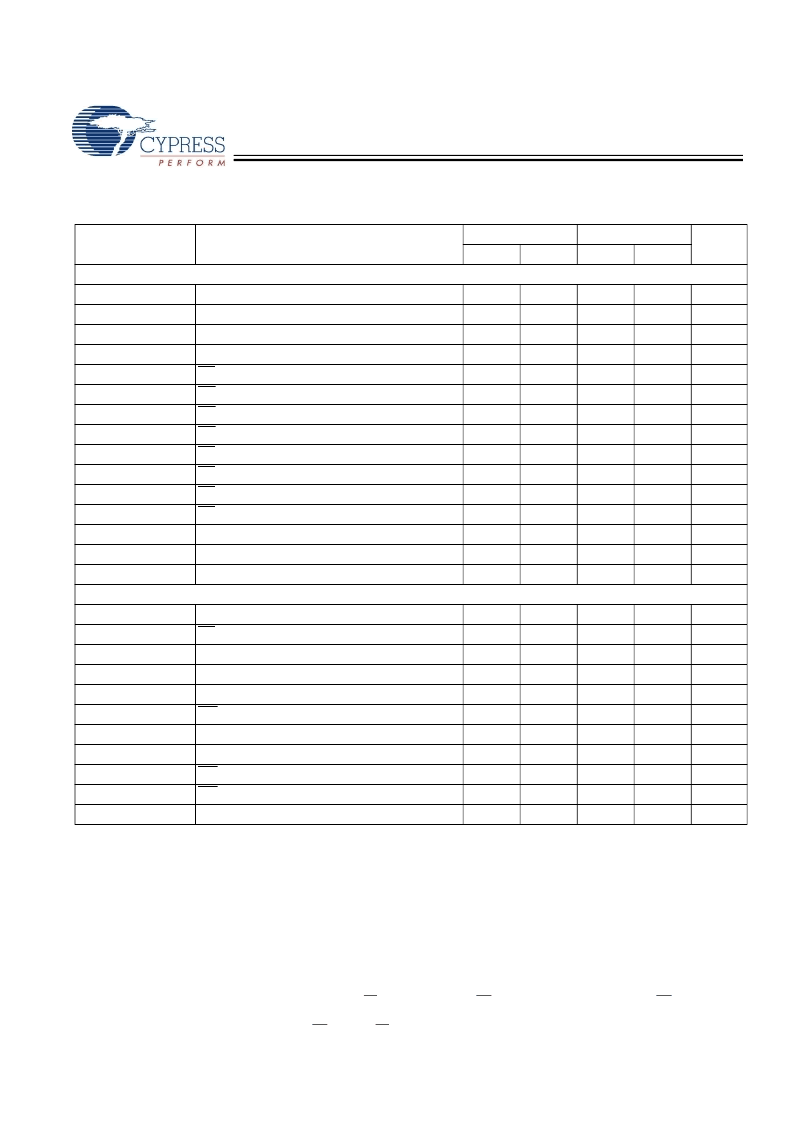

AC Switching Characteristics

(Over the Operating Range)

[6]

Parameter

Description

–10

–12

Unit

Min

Max

Min

Max

Read Cycle

t

power

t

RC

t

AA

t

OHA

t

ACE

t

DOE

t

LZOE

t

HZOE

t

LZCE

t

HZCE

t

PU

t

PD

t

DBE

t

LZBE

t

HZBE

Write Cycle

[10, 11]

V

CC

(typical) to the first access

[7]

Read Cycle Time

1

1

ms

10

12

ns

Address to Data Valid

10

12

ns

Data Hold from Address Change

3

3

ns

CE

1

LOW/CE

2

HIGH to Data Valid

OE LOW to Data Valid

10

12

ns

5

6

ns

OE LOW to Low-Z

OE HIGH to High-Z

[8]

CE

1

LOW/CE

2

HIGH to Low-Z

[8]

CE

1

HIGH/CE

2

LOW to High-Z

[8]

CE

1

LOW/CE

2

HIGH to Power Up

[9]

CE

1

HIGH/CE

2

LOW to Power Down

[9]

Byte Enable to Data Valid

1

1

ns

5

6

ns

3

3

ns

5

6

ns

0

0

ns

10

12

ns

5

6

ns

Byte Enable to Low-Z

1

1

ns

Byte Disable to High-Z

5

6

ns

t

WC

t

SCE

t

AW

t

HA

t

SA

t

PWE

t

SD

t

HD

t

LZWE

t

HZWE

t

BW

Write Cycle Time

10

12

ns

CE

1

LOW/CE

2

HIGH to Write End

Address Setup to Write End

7

8

ns

7

8

ns

Address Hold from Write End

0

0

ns

Address Setup to Write Start

0

0

ns

WE Pulse Width

7

8

ns

Data Setup to Write End

5.5

6

ns

Data Hold from Write End

WE HIGH to Low-Z

[8]

WE LOW to High-Z

[8]

0

0

ns

3

3

ns

5

6

ns

Byte Enable to End of Write

7

8

ns

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1061AV33-12ZXC | 16-Mbit (1M x 16) Static RAM |

| CY7C1061AV33-12ZXI | 16-Mbit (1M x 16) Static RAM |

| CY7C1061BV33 | 16-Mbit (1M x 16) Static RAM |

| CY7C1061BV33-10ZC | 16-Mbit (1M x 16) Static RAM |

| CY7C1061BV33-10ZI | 16-Mbit (1M x 16) Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1061AV33-10ZXIT | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1M x 16 CPG IND Fast Async 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1061AV33-12BAC | 制造商:Cypress Semiconductor 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| CY7C1061AV33-12ZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1061AV33-12ZCT | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY7C1061AV33-12ZI | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Single 3.3V 16M-Bit 1M x 16 12ns 54-Pin TSOP-II |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。