- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378507 > CY7C146-55JI (CYPRESS SEMICONDUCTOR CORP) 2Kx8 Dual-Port Static RAM PDF資料下載

參數(shù)資料

| 型號: | CY7C146-55JI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 2Kx8 Dual-Port Static RAM |

| 中文描述: | 2K X 8 DUAL-PORT SRAM, 55 ns, PQCC52 |

| 封裝: | PLASTIC, LCC-52 |

| 文件頁數(shù): | 1/18頁 |

| 文件大?。?/td> | 339K |

| 代理商: | CY7C146-55JI |

2Kx8 Dual-Port Static RAM

fax id: 5201

CY7C132/CY7C136

CY7C142/CY7C146

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

December 1989 – Revised March 27, 1997

1CY7C132/CY7C136

Features

True Dual-Ported memory cells which allow simulta-

neous reads of the same memory location

2K x 8 organization

0.65-micron CMOS for optimum speed/power

High-speed access: 15 ns

Low operating power: I

CC

= 90 mA (max.)

Fully asynchronous operation

Automatic power-down

Master CY7C132/CY7C136 easily expands data bus

width to 16 or more bits using slave CY7C142/CY7C146

BUSY output flag on CY7C132/CY7C136; BUSY input

on CY7C142/CY7C146

INT flag for port-to-port communication (52-pin

PLCC/PQFP versions)

Available in 48-pin DIP (CY7C132/142), 52-pin PLCC and

52-pin TQFP (CY7C136/146)

Pin-compatible and functionally equivalent to

IDT7132/IDT7142

Functional Description

The CY7C132/CY7C136/CY7C142 and CY7C146 are

high-speed CMOS 2K by 8 dual-port static RAMs. Two ports

are provided to permit independent access to any location in

memory. The CY7C132/ CY7C136 can be utilized as either a

standalone 8-bit dual-port static RAM or as a MASTER du-

al-port RAM in conjunction with the CY7C142/CY7C146

SLAVE dual-port device in systems requiring 16-bit or greater

word widths. It is the solution to applications requiring shared

or buffered data such as cache memory for DSP, bit-slice, or

multiprocessor designs.

Each port has independent control pins; chip enable (CE),

write enable (R/W), and output enable (OE). BUSY flags are

provided on each port. In addition, an interrupt flag (INT) is

provided on each port of the 52-pin PLCC version. BUSY sig-

nals that the port is trying to access the same location currently

being accessed by the other port. On the PLCC version, INT

is an interrupt flag indicating that data has been placed in a

unique location (7FF for the left port and 7FE for the right port).

An automatic power-down feature is controlled independently

on each port by the chip enable (CE) pins.

The CY7C132/CY7C142 are available in 48-pin DIP. The

CY7C136/CY7C146 are available in 52-pin PLCC and PQFP.

Notes:

1.

CY7C132/CY7C136 (Master): BUSY is open drain output and requires pull-up resistor.

CY7C142/CY7C146 (Slave): BUSY is input.

Open drain outputs; pull-up resistor required.

2.

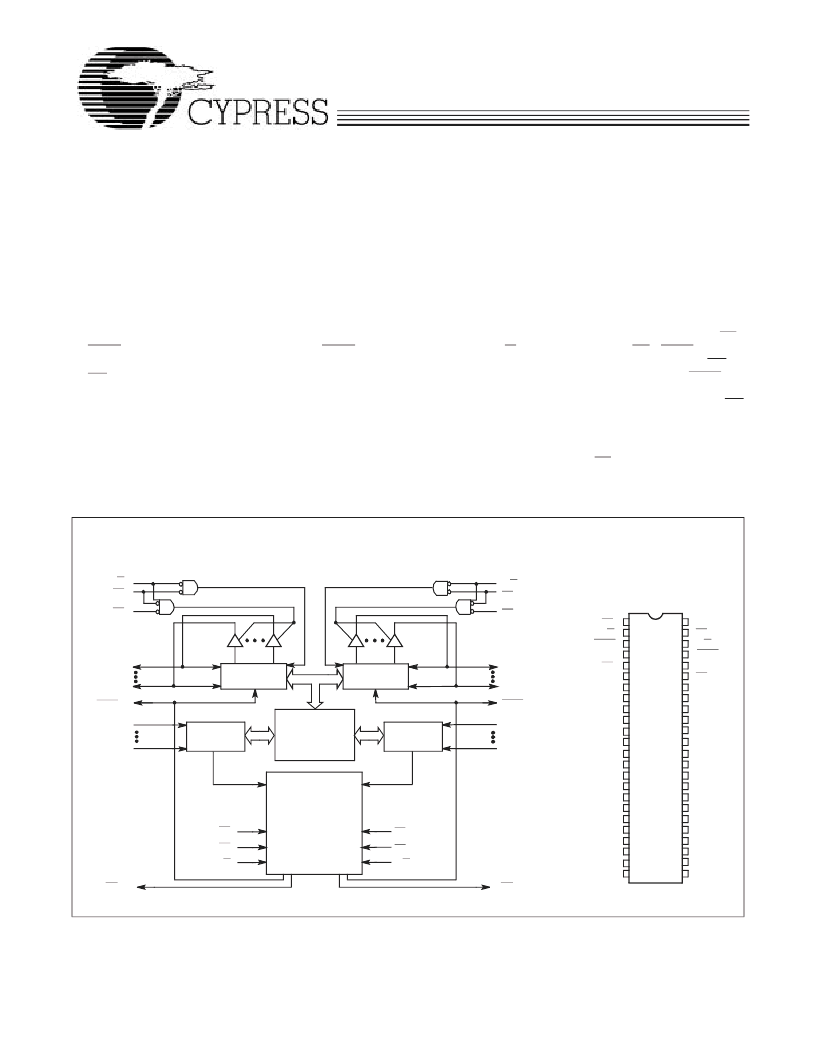

LogicBlock Diagram

Pin Configuration

C132-1

C132-2

13

14

15

16

17

18

19

20

21

22

23

24

26

25

27

28

32

31

30

29

33

36

35

34

GND

R/W

L

CE

L

BUSY

L[1]

OE

L

A

10L

A

0L

A

0R

A

10R

R/W

R

CE

R

OE

R

CE

R

OE

R

R/W

R

CE

L

OE

L

R/W

L

I/O

7L

I/O

0L

I/O

7R

I/O

0R

BUSY

R[1]

INT

L[2]

INT

R[2]

ARBITRATION

LOGIC

(7C132/7C136 ONLY)

AND

INTERRUPTLOGIC

(7C136/7C146 ONLY)

CONTROL

I/O

CONTROL

I/O

MEMORY

ARRAY

ADDRESS

DECODER

ADDRESS

DECODER

1

2

3

4

5

6

7

8

9

10

11

12

38

37

39

40

44

43

42

41

45

48

47

46

R/W

L

BUSY

L

A

10L

OE

L

A

0L

A

1L

A

2L

A

3L

A

4L

A

5L

A

6L

A

7L

A

8L

A

9L

I/O

0L

I/O

1L

I/O

2L

I/O

3L

I/O

4L

I/O

5L

I/O

6L

I/O

7L

CE

L

CE

R

R/W

R

BUSY

R

A

10R

OE

R

A

0R

A

1R

A

2R

A

3R

A

4R

A

5R

A

6R

A

7R

A

8R

A

9R

I/O

7R

I/O

6R

I/O

5R

I/O

4R

I/O

3R

I/O

2R

I/O

1R

I/O

0R

V

CC

DIP

Top View

7C132

7C142

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C146-55LMB | 2Kx8 Dual-Port Static RAM |

| CY7C146-55NC | 2Kx8 Dual-Port Static RAM |

| CY7C146-25NC | 2Kx8 Dual-Port Static RAM |

| CY7C136-15JC | Hook-Up Wire; Conductor Size AWG:20; No. Strands x Strand Size:7 x 28; Jacket Color:Dark Blue; Approval Bodies:UL, CSA; Approval Categories:UL AWM Styles 1007, 1565; CSA Types TR-64, TRSR-64; JQA-F; Passes VW-1 Flame Test RoHS Compliant: Yes |

| CY7C136-15NC | Hookup wire; Conductor Size AWG:20; No. Strands x Strand Size:10 x 30; Jacket Color:Black; Approval Bodies:UL, CSA; Conductor Material:Copper; Jacket Material:Polyvinylchloride (PVC); Leaded Process Compatible:Yes RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C146-55JXC | 功能描述:靜態(tài)隨機(jī)存取存儲器 5V 2Kx8 COM Dual Port 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C146-55JXCT | 功能描述:靜態(tài)隨機(jī)存取存儲器 5V 2Kx8 COM Dual Port 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C147 WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1470BV25-167AXC | 功能描述:靜態(tài)隨機(jī)存取存儲器 72MB (2Mx36) 2.5v 167MHz SRAm RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1470BV25-167AXCT | 功能描述:靜態(tài)隨機(jī)存取存儲器 2Mx 36, 2.5V NoBL PL 靜態(tài)隨機(jī)存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。