- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376562 > DAC8012FP 12-Bit Digital-to-Analog Converter PDF資料下載

參數(shù)資料

| 型號: | DAC8012FP |

| 英文描述: | 12-Bit Digital-to-Analog Converter |

| 中文描述: | 12位數(shù)字到模擬轉(zhuǎn)換器 |

| 文件頁數(shù): | 3/9頁 |

| 文件大小: | 211K |

| 代理商: | DAC8012FP |

3

DAC80/80P

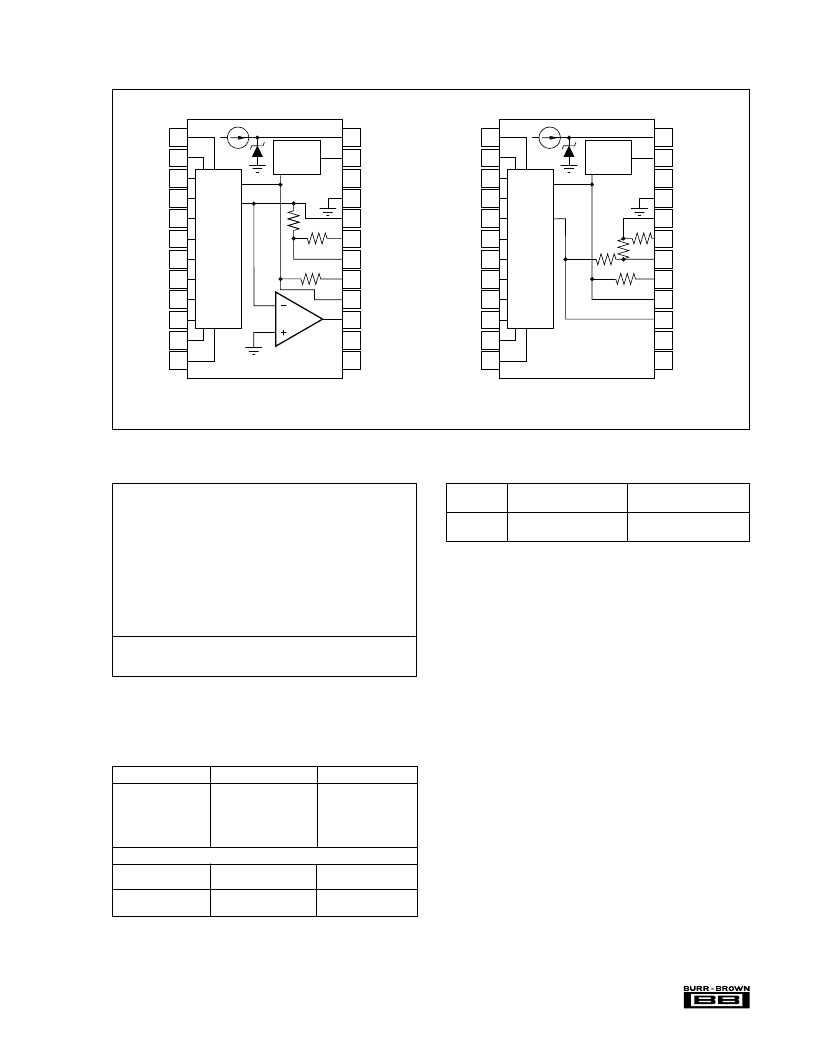

FUNCTIONAL DIAGRAM AND PIN ASSIGNMENTS

ABSOLUTE MAXIMUM RATINGS

PACKAGE INFORMATION

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix D of Burr-Brown IC Data Book.

PACKAGE DRAWING

NUMBER

(1)

MODEL

PACKAGE

DAC80P

DAC80

24-Pin Plastic DIP

24-Pin Ceramic DIP

167

125

+V

CC

to Common ...................................................................... 0V to +18V

–V

CC

to Common ......................................................................... 0V to –18

Digital Data Inputs to Common .............................................. –1V to +18V

Reference Output to Common ............................................................

±

V

CC

Reference Input to Common ...............................................................

±

V

CC

Bipolar Offset to Common...................................................................

±

V

CC

10V Range R to Common ...................................................................

±

V

CC

20V Range R to Common ...................................................................

±

V

CC

External Voltage to DAC Output .............................................. –5V to +5V

Lead Temperature (soldering, 10s)................................................ +300

°

C

Max Junction Temperature .............................................................. 165

°

C

Thermal Resistance,

θ

JA

: Plastic DIP ...........................................100

°

C/W

Ceramic DIP .........................................65

°

C/W

Stresses above those listed under “Absolute Maximum Ratings” may

cause permanent damage to the device. Exposure to absolute maxi-

mum conditions for extended periods may affect device reliability.

NOTE: (1) Logic supply applied to this pin has no effect.

(MSB) Bit 1

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

Bit 8

Bit 9

Bit 10

Bit 11

(LSB) Bit 12

6.3V Ref Out

Gain Adjust

+V

CC

Common

Summing Junction

20V Range

10V Range

Bipolar Offset

Ref Input

V

OUT

–V

CC

NC

(1)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Reference

Control

Circuit

12-Bit

Resistor

Ladder

Network

and

Current

Switches

(MSB) Bit 1

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

Bit 8

Bit 9

Bit 10

Bit 11

(LSB) Bit 12

6.3V Ref Out

Gain Adjust

+V

CC

Common

Scaling Network

Scaling Network

Scaling Network

Bipolar Offset

Ref Input

I

OUT

–V

CC

NC

(1)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Reference

Control

Circuit

12-Bit

Resistor

Ladder

Network

and

Current

Switches

Voltage Models

Current Models

5k

5k

6.3k

2k

3k

6.3k

5k

BURN-IN SCREENING

Burn-in screening is an option available for the models

indicated in the Ordering Information table. Burn-in dura-

tion is 160 hours at the maximum specified grade operating

temperature (or equivalent combination of time and tem-

perature).

All units are tested after burn-in to ensure that grade speci-

fications are met. To order burn-in, add “–BI” to the base

model number.

ORDERING INFORMATION

MODEL

PACKAGE

OUTPUT

DAC80-CBI-I

DAC80Z-CBI-I

DAC80-CBI-V

DAC80Z-CBI-V

DAC80P-CBI-V

Ceramic DIP

Ceramic DIP

Ceramic DIP

Ceramic DIP

Plastic DIP

Current

Current

Voltage

Voltage

Voltage

BURN-IN SCREENING OPTION

BURN-IN TEMP.

(160h)

(1)

+125

°

C

+125

°

C

MODEL

PACKAGE

DAC80-CBI-V-BI

DAC80P-CBI-V-BI

Ceramic DIP

Plastic DIP

NOTE: (1) Or equivalent combination. See text.

相關PDF資料 |

PDF描述 |

|---|---|

| DAC8012FPC | 12-Bit Digital-to-Analog Converter |

| DAC8012FR | 12-Bit Digital-to-Analog Converter |

| DAC8012GP | 12-Bit Digital-to-Analog Converter |

| DAC8012HP | 12-Bit Digital-to-Analog Converter |

| DAC8012JU-BI | 12-Bit Digital-to-Analog Converter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DAC8012FPC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DAC8012FR | 制造商:Analog Devices 功能描述: |

| DAC8012GP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DAC8012HP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DAC8012HPC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。