- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19028 > DC1525A-D (Linear Technology)BOARD DEMO 65MSPS LTC2172-14 PDF資料下載

參數(shù)資料

| 型號(hào): | DC1525A-D |

| 廠商: | Linear Technology |

| 文件頁數(shù): | 32/34頁 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO 65MSPS LTC2172-14 |

| 軟件下載: | QuikEval II System |

| 設(shè)計(jì)資源: | DC1525A Design Files |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

| 相關(guān)產(chǎn)品: | DC1371A-ND - BOARD USB DATA ACQUISITION HS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁

LTC2172-14/

LTC2171-14/LTC2170-14

7

21721014fb

SYMBOL PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

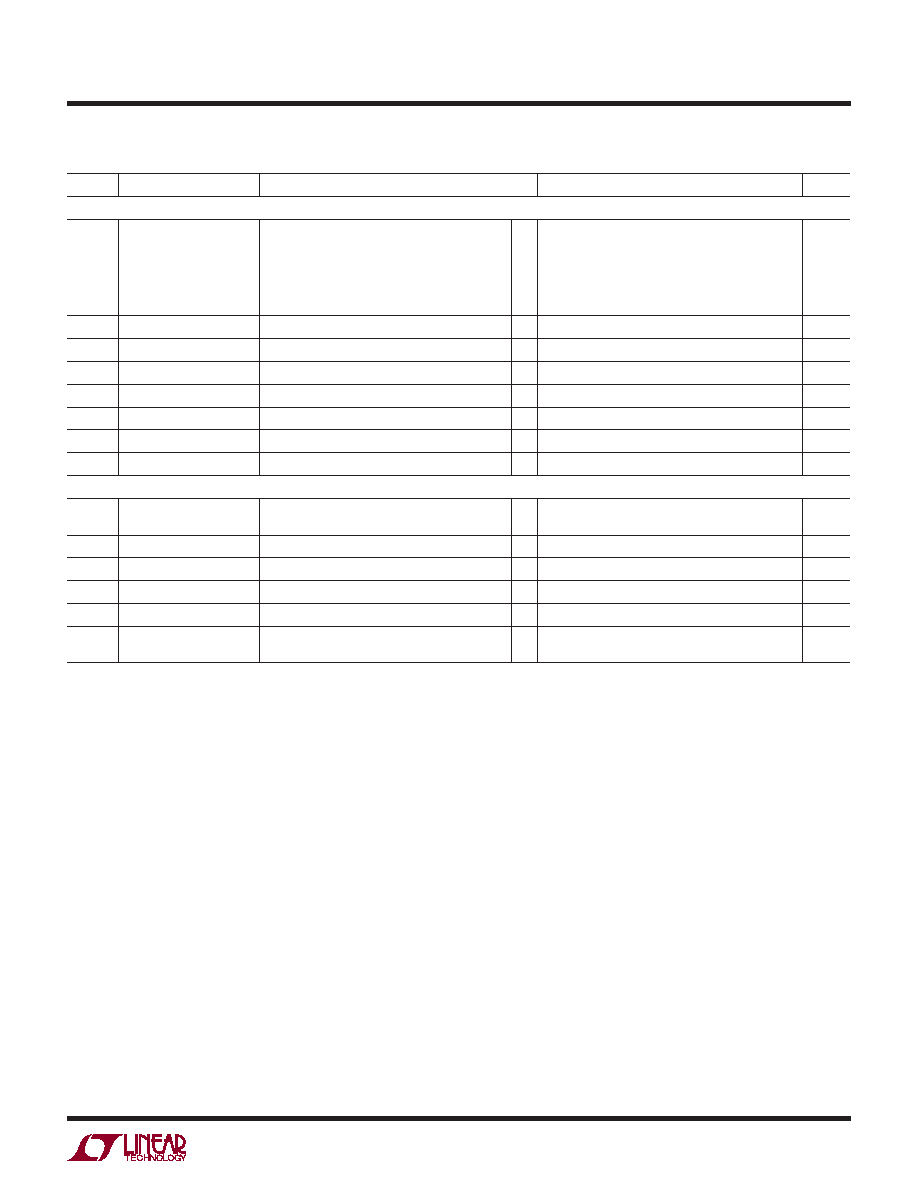

Digital Data Outputs (RTERM = 100Ω Differential, CL = 2pF to GND on Each Output)

tSER

Serial Data Bit Period

2-Lanes, 16-Bit Serialization

2-Lanes, 14-Bit Serialization

2-Lanes, 12-Bit Serialization

1-Lane, 16-Bit Serialization

1-Lane, 14-Bit Serialization

1-Lane, 12-Bit Serialization

1 / (8 fS)

1 / (7 fS)

1 / (6 fS)

1 / (16 fS)

1 / (14 fS)

1 / (12 fS)

s

tFRAME

FR to DCO Delay

(Note 8)

l

0.35 tSER

0.5 tSER

0.65 tSER

s

tDATA

DATA to DCO Delay

(Note 8)

l

0.35 tSER

0.5 tSER

0.65 tSER

s

tPD

Propagation Delay

(Note 8)

l

0.7n + 2 tSER 1.1n + 2 tSER 1.5n + 2 tSER

s

tR

Output Rise Time

Data, DCO, FR, 20% to 80%

0.17

ns

tF

Output Fall Time

Data, DCO, FR, 20% to 80%

0.17

ns

DCO Cycle-to-Cycle Jitter tSER = 1ns

60

psP-P

Pipeline Latency

6

Cycles

SPI Port Timing (Note 8)

tSCK

SCK Period

Write Mode

Readback Mode, CSDO = 20pF, RPULLUP = 2k

l

40

250

ns

tS

CS to SCK Set-Up Time

l

5

ns

tH

SCK to CS Set-Up Time

l

5

ns

tDS

SDI Set-Up Time

l

5

ns

tDH

SDI Hold Time

l

5

ns

tDO

SCK Falling to SDO Valid

Readback Mode

CSDO = 20pF, RPULLUP = 2k

l

125

ns

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: All voltage values are with respect to GND with GND and OGND

shorted (unless otherwise noted).

Note 3: When these pin voltages are taken below GND or above VDD, they

will be clamped by internal diodes. This product can handle input currents

of greater than 100mA below GND or above VDD without latchup.

Note 4: When these pin voltages are taken below GND they will be

clamped by internal diodes. When these pin voltages are taken above VDD

they will not be clamped by internal diodes. This product can handle input

currents of greater than 100mA below GND without latchup.

Note 5: VDD = OVDD = 1.8V, fSAMPLE = 65MHz (LTC2172),

40MHz (LTC2171), or 25MHz (LTC2170), 2-lane output mode, differential

ENC+/ENC– = 2VP-P sine wave, input range = 2VP-P with differential drive,

unless otherwise noted.

Note 6: Integral nonlinearity is defined as the deviation of a code from a

best fit straight line to the transfer curve. The deviation is measured from

the center of the quantization band.

Note 7: Offset error is the offset voltage measured from –0.5 LSB when

the output code flickers between 00 0000 0000 0000 and 11 1111 1111

1111 in 2’s complement output mode.

Note 8: Guaranteed by design, not subject to test.

Note 9: VDD = OVDD = 1.8V, fSAMPLE = 65MHz (LTC2172), 40MHz

(LTC2171), or 25MHz (LTC2170), 2-lane output mode, ENC+ = single-

ended 1.8V square wave, ENC– = 0V, input range = 2VP-P with differential

drive, unless otherwise noted. The supply current and power dissipation

specifications are totals for the entire chip, not per channel.

Note 10: Recommended operating conditions.

Note 11: The maximum sampling frequency depends on the speed grade

of the part and also which serialization mode is used. The maximum serial

data rate is 1000Mbps, so tSER must be greater than or equal to 1ns.

Note 12: Near-channel crosstalk refers to Ch. 1 to Ch.2, and Ch.3 to Ch.4.

Far-channel crosstalk refers to Ch.1 to Ch.3, Ch.1 to Ch.4, Ch.2 to Ch.3, and

Ch.2 to Ch.4.

TiMing characTerisTics The

l

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SM2450M | LAMP T1.25 TELE SLIDE 24V .05A |

| SM6020L | LAMP T-1.5 TELE SLIDE 60V .02A |

| SM3650L | LAMP T-1.5 TELE SLIDE 36V .08A |

| VX-5-1A3 | SWITCH BASIC SPDT 5A .187QC |

| SM3620L | LAMP T-1.5 TELE SLIDE 36V .02A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DC1525A-E | 功能描述:BOARD DEMO 40MSPS LTC2171-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-F | 功能描述:BOARD DEMO 25MSPS LTC2170-14 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-G | 功能描述:BOARD DEMO 125MSPS LTC2175-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-H | 功能描述:BOARD DEMO 105MSPS LTC2174-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

| DC1525A-I | 功能描述:BOARD DEMO 80MSPS LTC2173-12 RoHS:是 類別:未定義的類別 >> 其它 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* 其它名稱:MS305720A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。