- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376711 > DG529DN (MAXIM INTEGRATED PRODUCTS INC) 8-Channel Latchable Multiplexers PDF資料下載

參數(shù)資料

| 型號(hào): | DG529DN |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 運(yùn)動(dòng)控制電子 |

| 英文描述: | 8-Channel Latchable Multiplexers |

| 中文描述: | 4-CHANNEL, DIFFERENTIAL MULTIPLEXER, PQCC20 |

| 封裝: | PLASTIC, LCC-20 |

| 文件頁數(shù): | 12/16頁 |

| 文件大小: | 308K |

| 代理商: | DG529DN |

12-12

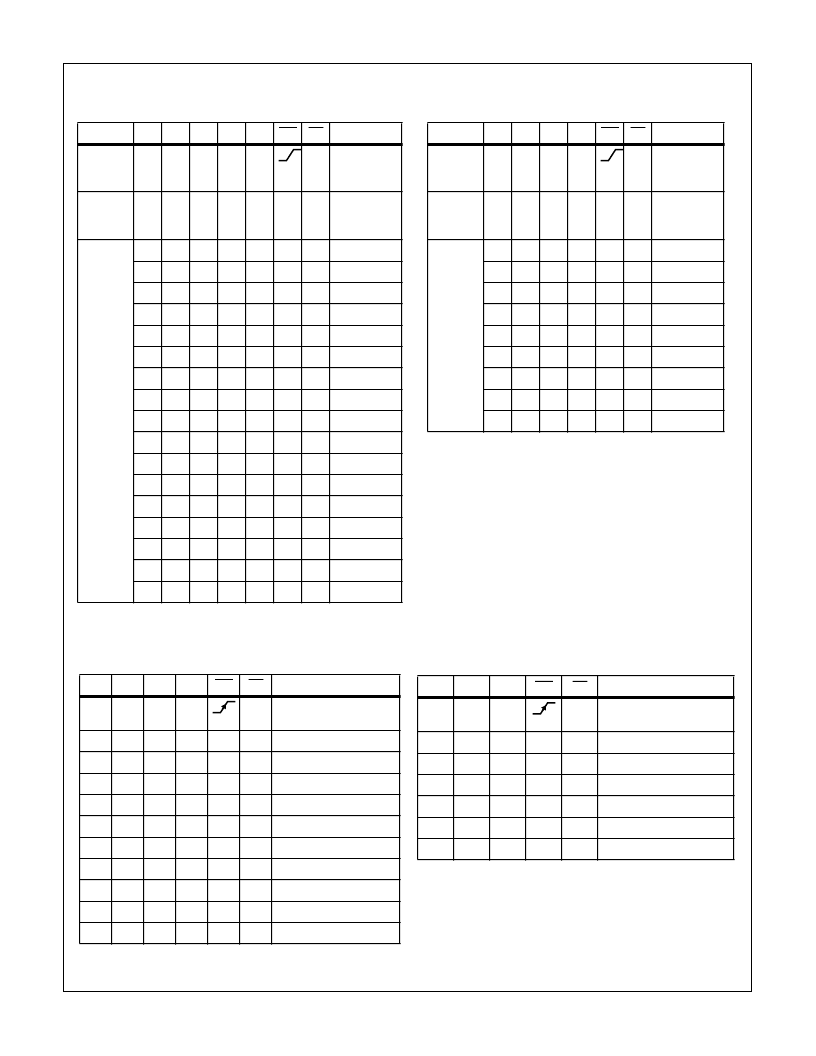

Truth Tables

DG526

A

3

A

2

A

1

A

0

EN

WR

RS

ON SWITCH

Latching

X

X

X

X

X

1

Maintains

Previous

Switch State

Reset

X

X

X

X

X

X

0

None

(Latches

Cleared)

Trans-

parent

Operation

X

X

X

X

0

0

1

None

0

0

0

0

1

0

1

1

0

0

0

1

1

0

1

2

0

0

1

0

1

0

1

3

0

0

1

1

1

0

1

4

0

1

0

0

1

0

1

5

0

1

0

1

1

0

1

6

0

1

1

0

1

0

1

7

0

1

1

1

1

0

1

8

1

0

0

0

1

0

1

9

1

0

0

1

1

0

1

10

1

0

1

0

1

0

1

11

1

0

1

1

1

0

1

12

1

1

0

0

1

0

1

13

1

1

0

1

1

0

1

14

1

1

1

0

1

0

1

15

1

1

1

1

1

0

1

16

Logic “0” = V

AL

, V

ENL

≤

0.8V

DG528

A

2

A

1

A

0

EN

WR

RS

ON SWITCH

X

X

X

X

1

Maintains Previous

Switch Condition

X

X

X

X

X

0

None (Latches Cleared)

X

X

X

0

0

1

None

0

0

0

1

0

1

1

0

0

1

1

0

1

2

0

1

0

1

0

1

3

0

1

1

1

0

1

4

1

0

0

1

0

1

5

1

0

1

1

0

1

6

1

1

0

1

0

1

7

1

1

1

1

0

1

8

DG527

A

2

A

1

A

0

EN

WR

RS

ON SWITCH

Latching

X

X

X

X

1

Maintains

Previous

Switch State

Reset

X

X

X

X

X

0

None

(Latches

Cleared)

Trans-

parent

Operation

X

X

X

0

0

1

None

0

0

0

1

0

1

1

0

0

1

1

0

1

2

0

1

0

1

0

1

3

0

1

1

1

0

1

4

1

0

0

1

0

1

5

1

0

1

1

0

1

6

1

1

0

1

0

1

7

1

1

1

1

0

1

8

Logic “1” = V

AH

, V

ENH

≥

2.4V

DG529

A

1

A

0

EN

WR

RS

ON SWITCH

X

X

X

1

Maintains Previous Switch

Condition

X

X

X

X

0

None (Latches Cleared)

X

X

0

0

1

None

0

0

1

0

1

1

0

1

1

0

1

2

1

0

1

0

1

3

1

1

1

0

1

4

Logic “1”: V

AH

≥

2.4V

Logic “0”: V

AL

≤

0.8V

DG526, DG527, DG528, DG529

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。