- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376726 > DJIXF972MTCA4 (Intel Corp.) Single-Port 10/100 Mbps PHY Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | DJIXF972MTCA4 |

| 廠商: | Intel Corp. |

| 英文描述: | Single-Port 10/100 Mbps PHY Transceiver |

| 中文描述: | 單端口10/100 Mbps的物理層收發(fā)器 |

| 文件頁(yè)數(shù): | 79/92頁(yè) |

| 文件大小: | 666K |

| 代理商: | DJIXF972MTCA4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)當(dāng)前第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

Intel

LXT972M Single-Port 10/100 Mbps PHY Transceiver

Datasheet

Document Number: 302875-005

Revision Date: 27-Oct-2005

79

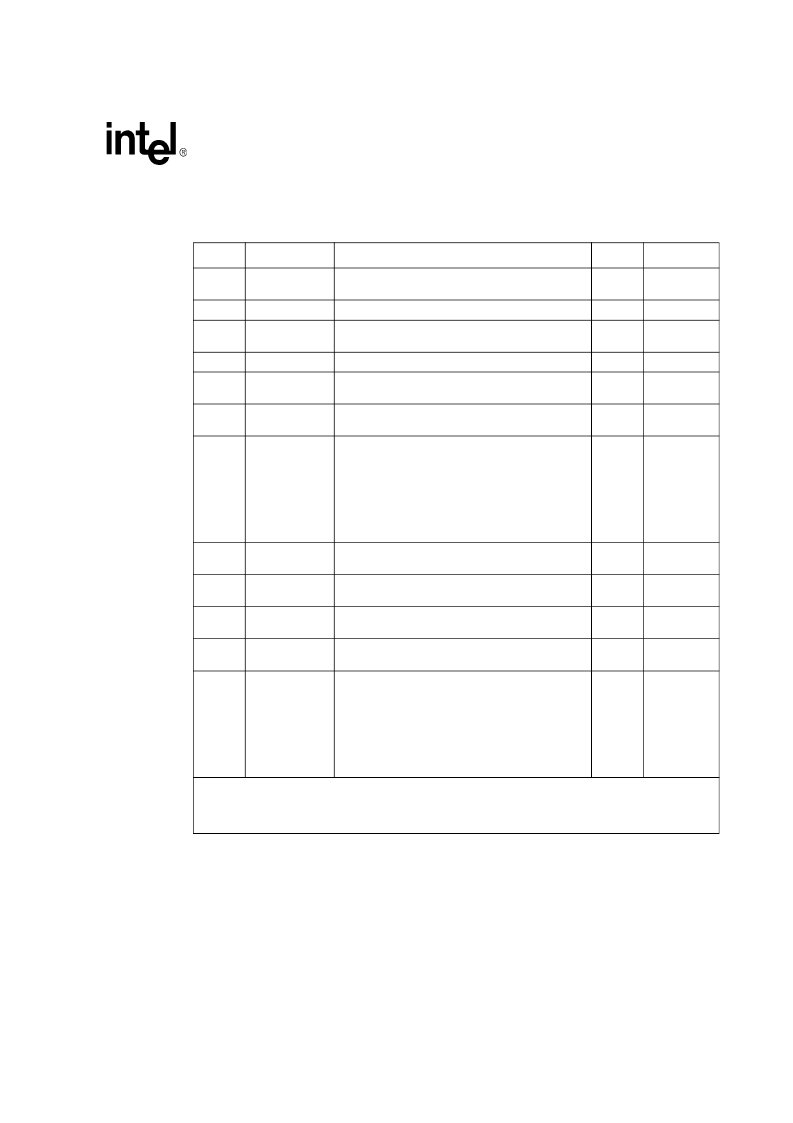

Table 45

lists auto-negotiation advertisement bits.

Table 45. Auto-Negotiation Advertisement Register - Address 4, Hex 4

Bit

Name

Description

Type

1

Default

4.15

Next Page

0 = Port has no ability to send multiple pages.

1 = Port has ability to send multiple pages.

R/W

0

4.14

Reserved

Ignore when read.

RO

0

4.13

Remote Fault

0 = No remote fault.

1 = Remote fault.

R/W

0

4.12

Reserved

Write as ‘0’. Ignore on Read.

R/W

0

4.11

Asymmetric

Pause

Pause operation defined in IEEE 802.3 Standard,

Clause 40 and 27

R/W

0

4.10

Pause

0 = Pause operation disabled.

1 = Pause operation enabled for full-duplex links

R/W

0

4.9

100BASE-T4

0 = 100BASE-T4 capability is not available.

1 = 100BASE-T4 capability is available.

NOTE:

The LXT972M Transceiver does not

support 100BASE-T4 but allows this bit to

be set to advertise in the auto-negotiation

sequence for 100BASE-T4 operation. An

external 100BASE-T4 transceiver can be

switched in if this capability is desired.

R/W

0

4.8

100BASE-TX

full-duplex

0 = Port is not 100BASE-TX full-duplex capable.

1 = Port is 100BASE-TX full-duplex capable.

R/W

Note 2

4.7

100BASE-TX

0 = Port is not 100BASE-TX capable.

1 = Port is 100BASE-TX capable.

R/W

Note 2

4.6

10BASE-T

full-duplex

0 = Port is not 10BASE-T full-duplex capable.

1 = Port is 10BASE-T full-duplex capable.

R/W

Note 2

4.5

10BASE-T

0 = Port is not 10BASE-T capable.

1 = Port is 10BASE-T capable.

R/W

Note 2

4.4:0

Selector Field,

S<4:0>

<00001> = IEEE 802.3.

<00010> = IEEE 802.9 ISLAN-16T.

<00000> = Reserved for future auto-negotiation

development.

<11111> = Reserved for future auto-negotiation

development.

NOTE:

Unspecified or reserved combinations must

not be transmitted.

R/W

00001

1. R/W = Read/Write

RO = Read Only

2. Some bits have their default values determined at reset by hardware configuration pins. For default details

for these bits, see

Section 5.4.4, “Hardware Configuration Settings”

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DJIXF972MTEA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXP972MBAA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXP972MBCA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXP972MBEA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJIXP972MCAA4 | Single-Port 10/100 Mbps PHY Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DJIXF972MTEA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJIXFEAD0QE000 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

| DJIXFEAD0QE001 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

| DJIXFEAD0SE000 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

| DJIXFEAD0SE001 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 8-Port 10/100 Mbps PHY Transceivers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。