- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376725 > DJLXT972MBAA4 (Intel Corp.) Single-Port 10/100 Mbps PHY Transceiver PDF資料下載

參數(shù)資料

| 型號: | DJLXT972MBAA4 |

| 廠商: | Intel Corp. |

| 英文描述: | Single-Port 10/100 Mbps PHY Transceiver |

| 中文描述: | 單端口10/100 Mbps的物理層收發(fā)器 |

| 文件頁數(shù): | 77/92頁 |

| 文件大?。?/td> | 666K |

| 代理商: | DJLXT972MBAA4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Intel

LXT972M Single-Port 10/100 Mbps PHY Transceiver

Datasheet

Document Number: 302875-005

Revision Date: 27-Oct-2005

77

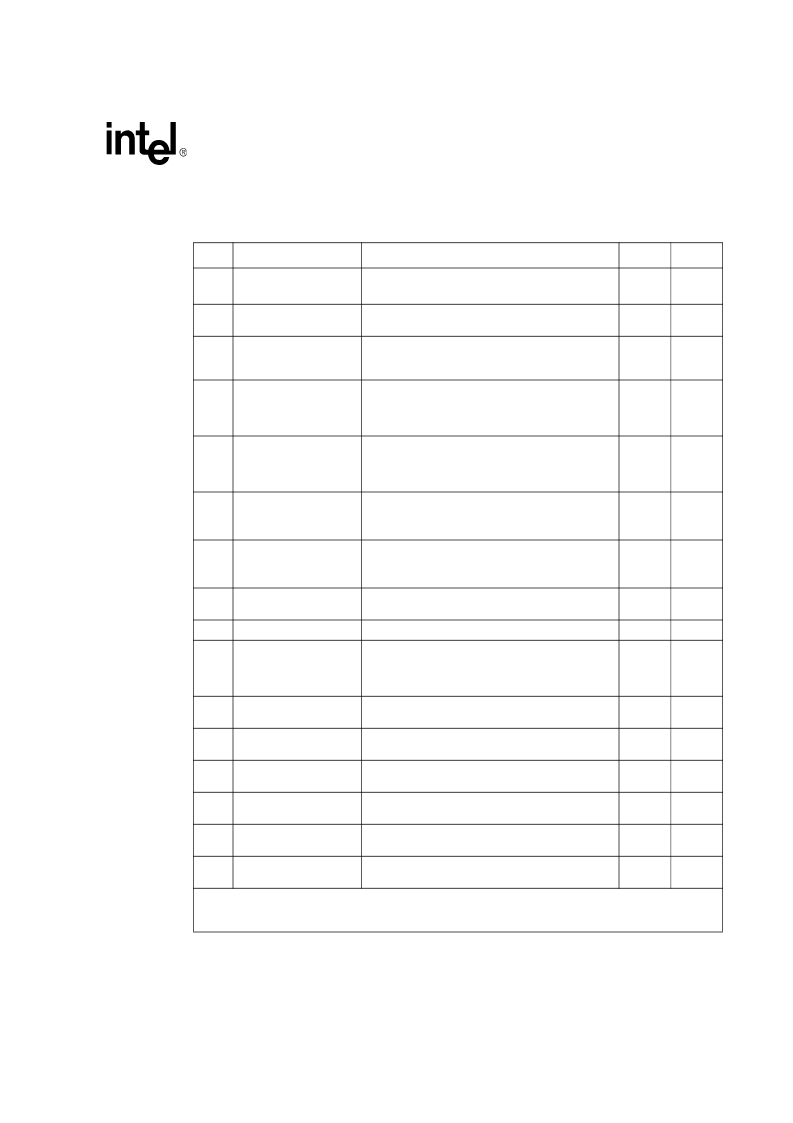

Table 42

lists MII status register bits.

Table 42. MII Status Register #1 - Address 1, Hex 1

Bit

Name

Description

Type

1

Default

1.15

100BASE-T4

Not Supported

0 = PHY not able to perform 100BASE-T4

1 = PHY able to perform 100BASE-T4

RO

0

1.14

100BASE-X Full-Duplex

0 = PHY not able to perform full-duplex 100BASE-X

1 = PHY able to perform full-duplex 100BASE-X

RO

1

1.13

100BASE-X Half-Duplex

0 = PHY not able to perform half-duplex

100BASE-X

1 = PHY able to perform half-duplex 100BASE-X

RO

1

1.12

10 Mbps Full-Duplex

0 = PHY not able to operate at 10 Mbps full-duplex

mode

1 = PHY able to operate at 10 Mbps in full-duplex

mode

RO

1

1.11

10 Mbps Half-Duplex

0 = PHY not able to operate at 10 Mbps in half-

duplex

1 = PHY able to operate at 10 Mbps in half-duplex

mode

RO

1

1.10

100BASE-T2 Full-

Duplex

Not Supported

0 = PHY not able to perform full-duplex

100BASE-T2

1 = PHY able to perform full-duplex 100BASE-T2

RO

0

1.9

100BASE-T2 Half-

Duplex

Not Supported

0 = PHY not able to perform half-duplex

100BASE-T2

1 = PHY able to perform half-duplex 100BASE-T2

RO

0

1.8

Extended Status

0 = No extended status information in register 15

1 = Extended status information in register 15

RO

0

1.7

Reserved

Ignore when read.

RO

0

1.6

MF Preamble

Suppression

0 = PHY cannot accept management frames with

preamble suppressed

1 = PHY accepts management frames with

preamble suppressed

RO

0

1.5

Auto-Negotiation

complete

0 = Auto-negotiation not complete

1 = Auto-negotiation complete

RO

0

1.4

Remote Fault

0 = No remote fault condition detected

1 = Remote fault condition detected

RO/LH

0

1.3

Auto-Negotiation Ability

0 = PHY is not able to perform auto-negotiation

1 = PHY is able to perform auto-negotiation

RO

1

1.2

Link Status

0 = Link is down

1 = Link is up

RO/LL

0

1.1

Jabber Detect

0 = Jabber condition not detected

1 = Jabber condition detected

RO/LH

0

1.0

Extended Capability

0 = Basic register capabilities

1 = Extended register capabilities

RO

1

1. RO = Read Only

LL = Latching Low

LH = Latching High

相關PDF資料 |

PDF描述 |

|---|---|

| DJLXT972MBCA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MBEA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCAA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCCA4 | Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCEA4 | Single-Port 10/100 Mbps PHY Transceiver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DJLXT972MBCA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MBEA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCAA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCCA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

| DJLXT972MCEA4 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Single-Port 10/100 Mbps PHY Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復。