- 您現(xiàn)在的位置:買賣IC網 > PDF目錄376778 > DM7490AN (FAIRCHILD SEMICONDUCTOR CORP) Decade and Binary Counters PDF資料下載

參數(shù)資料

| 型號: | DM7490AN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Decade and Binary Counters |

| 中文描述: | TTL/H/L SERIES, ASYN NEGATIVE EDGE TRIGGERED 3-BIT UP DECADE COUNTER, PDIP14 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-14 |

| 文件頁數(shù): | 4/5頁 |

| 文件大?。?/td> | 47K |

| 代理商: | DM7490AN |

www.fairchildsemi.com

4

D

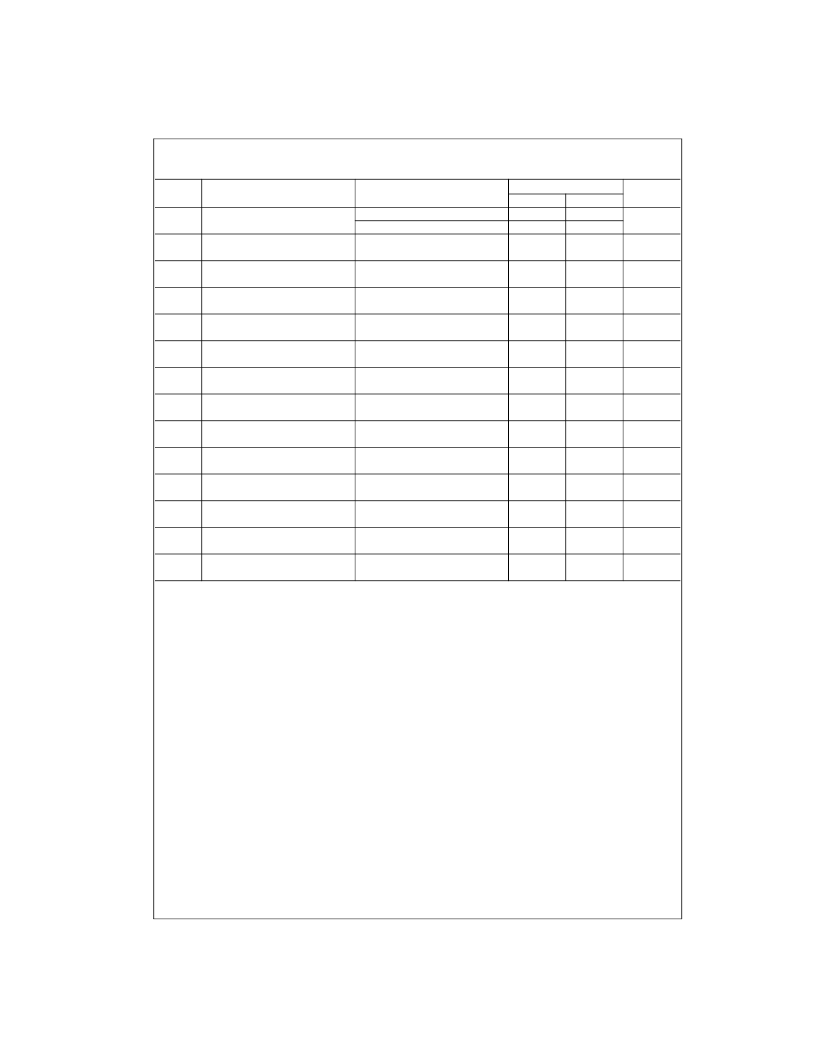

AC Switching Characteristics

at V

CC

=

5V and T

A

=

25

°

C

Symbol

Parameter

From (Input)

R

L

=

400

, C

L

=

15 pF

Min

32

16

Units

To (Output)

A to Q

A

B to Q

B

Max

f

MAX

Maximum Clock

Frequency

Propagation Delay Time

MHz

t

PLH

A to Q

A

16

ns

LOW-to-HIGH Level Output

Propagation Delay Time

HIGH-to-LOW Level Output

t

PHL

A to Q

A

18

ns

t

PLH

Propagation Delay Time

LOW-to-HIGH Level Output

Propagation Delay Time

A to Q

D

48

ns

t

PHL

A to Q

D

50

ns

HIGH-to-LOW Level Output

Propagation Delay Time

LOW-to-HIGH Level Output

t

PLH

B to Q

B

16

ns

t

PHL

Propagation Delay Time

HIGH-to-LOW Level Output

Propagation Delay Time

B to Q

B

21

ns

t

PLH

B to Q

C

32

ns

LOW-to-HIGH Level Output

Propagation Delay Time

HIGH-to-LOW Level Output

t

PHL

B to Q

C

35

ns

t

PLH

Propagation Delay Time

LOW-to-HIGH Level Output

Propagation Delay Time

B to Q

D

32

ns

t

PHL

B to Q

D

35

ns

HIGH-to-LOW Level Output

Propagation Delay Time

LOW-to-HIGH Level Output

t

PLH

SET-9 to Q

A

, Q

D

30

ns

t

PHL

Propagation Delay Time

HIGH-to-LOW Level Output

Propagation Delay Time

SET-9 to Q

B

, Q

C

40

ns

t

PHL

SET-0

40

ns

HIGH-to-LOW Level Output

Any Q

相關PDF資料 |

PDF描述 |

|---|---|

| DM74ALS00 | Quad 2-Input NAND Gate |

| DM74ALS00AM | Quad 2-Input NAND Gate |

| DM74ALS00AN | Low-Offset Voltage Operational Amplifier 8-SOIC 0 to 70 |

| DM74ALS00ASJ | Low-Offset Voltage Operational Amplifier 8-SOIC 0 to 70 |

| DM74ALS00A | Quad 2-Input NAND Gate(四2輸入與非門) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DM7490AN/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Asynchronous Up Counter |

| DM7490AN/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Asynchronous Up Counter |

| DM7491AN | 制造商:Texas Instruments 功能描述: |

| DM7492AJ/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Asynchronous Up Counter |

| DM7492AN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Asynchronous Up Counter |

發(fā)布緊急采購,3分鐘左右您將得到回復。