- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376779 > DM74ALS109AN (FAIRCHILD SEMICONDUCTOR CORP) Dual J-K Positive-Edge-Triggered Flip-Flop PDF資料下載

參數(shù)資料

| 型號(hào): | DM74ALS109AN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual J-K Positive-Edge-Triggered Flip-Flop |

| 中文描述: | ALS SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP16 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-16 |

| 文件頁(yè)數(shù): | 1/6頁(yè) |

| 文件大小: | 55K |

| 代理商: | DM74ALS109AN |

2000 Fairchild Semiconductor Corporation

DS006196

www.fairchildsemi.com

April 1984

Revised February 2000

D

DM74ALS109A

Dual J-K Positive-Edge-Triggered Flip-Flop

with Preset and Clear

General Description

The DM74ALS109A is a dual edge-triggered flip-flop. Each

flip-flop has individual J, K, clock, clear and preset inputs,

and also complementary Q and Q outputs.

Information at input J or K is transferred to the Q output on

the positive going edge of the clock pulse. Clock triggering

occurs at a voltage level of the clock pulse and is not

directly related to the transition time of the positive going

pulse. When the clock input is at either the HIGH or LOW

level, the J, K input signal has no effect.

Asynchronous preset and clear inputs will set or clear Q

output respectively upon the application of low level signal.

The J-K design allows operation as a D flip-flop by tying the

J and K inputs together.

Features

I

Switching specifications at 50 pF

I

Switching specifications guaranteed over full tempera-

ture and V

CC

range

I

Advanced oxide-isolated, ion-implanted Schottky TTL

process

I

Functionally and pin for pin compatible with Schottky

and LS TTL counterpart

I

Improved AC performance over LS109 at approximately

half the power

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

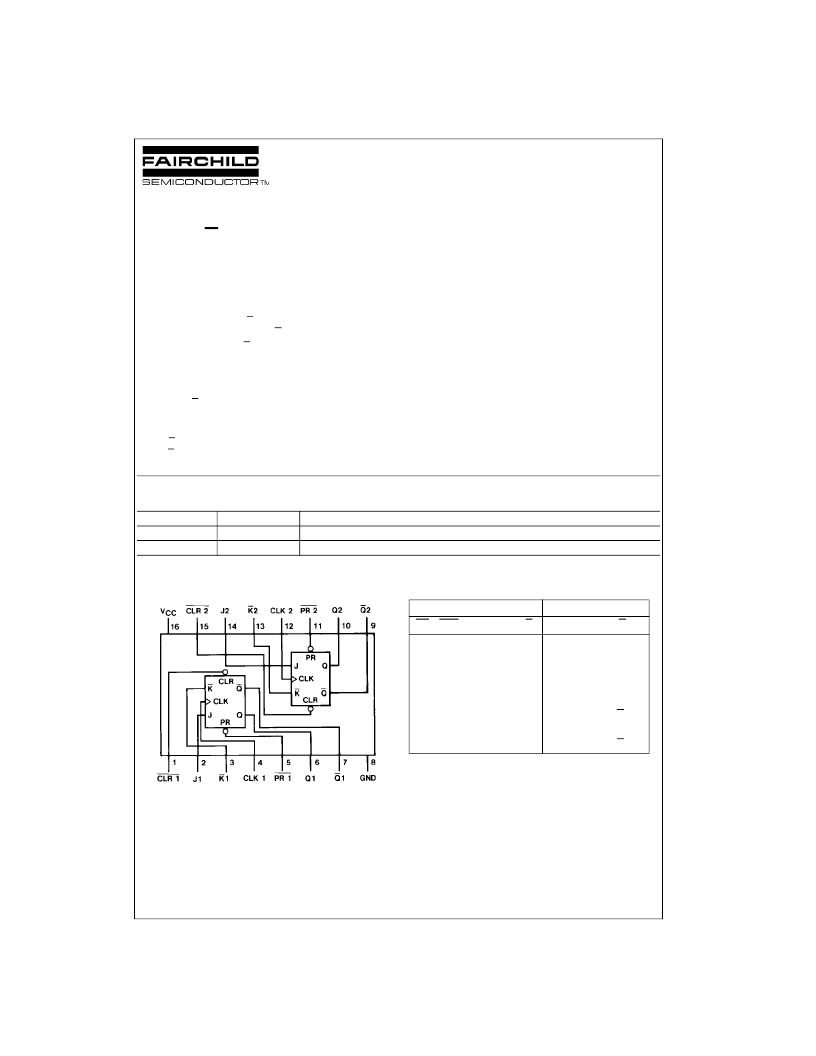

Connection Diagram

Function Table

L

=

LOW State

H

=

HIGH State

X

=

Don't Care

↑

=

Positive Edge Transition,

Q

0

=

Previous Condition of Q

Note 1:

This condition is nonstable; it will not persist when present and

clear inputs return to their inactive (HIGH) level. The output levels in this

condition are not guaranteed to meet the V

OH

specification.

Order Number

DM74ALS109AM

DM74ALS109AN

Package Number

M16A

N16E

Package Description

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs

Outputs

PR

L

H

L

H

H

CLR

H

L

L

H

H

CK

X

X

X

↑

↑

↑

↑

L

J

X

X

X

L

H

K

X

X

X

L

L

Q

H

L

Q

L

H

H (Note 1)

L

H (Note 1)

H

TOGGLE

H

H

H

H

H

H

L

H

X

H

H

X

Q

0

H

Q

0

Q

0

L

Q

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM74ALS10AM | Replaced by SN74LVC652A : Octal Bus Transceiver And Register With 3-State Outputs 24-SOIC -40 to 85 |

| DM74ALS10A | Triple 3-Input NAND Gate(三3輸入與非門) |

| DM74ALS10AN | Replaced by SN74LVC652A : Octal Bus Transceiver And Register With 3-State Outputs 24-SOIC -40 to 85 |

| DM74ALS10ASJ | Triple 3-Input NAND Gate |

| DM74ALS10AMX | Triple 3-input NAND Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM74ALS109AN/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:J-K-Type Flip-Flop |

| DM74ALS109AN/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:J-K-Type Flip-Flop |

| DM74ALS109AN_Q | 功能描述:觸發(fā)器 Dl J-K Flip-Flop RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| DM74ALS109ANX | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual J-K Positive-Edge-Triggered Flip-Flop |

| DM74ALS109J/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:J-K-Type Flip-Flop |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。