- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376802 > DM9000AE (Electronic Theatre Controls, Inc.) Ethernet Controller with General Processor Interface PDF資料下載

參數(shù)資料

| 型號: | DM9000AE |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Ethernet Controller with General Processor Interface |

| 中文描述: | 以太網(wǎng)控制器與通用處理器接口 |

| 文件頁數(shù): | 15/56頁 |

| 文件大?。?/td> | 1744K |

| 代理商: | DM9000AE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

DM9000A

Ethernet Controller with General Processor Interface

Preliminary datasheet

Version: DM9000A-DS-P03

Apr. 21, 2005

15

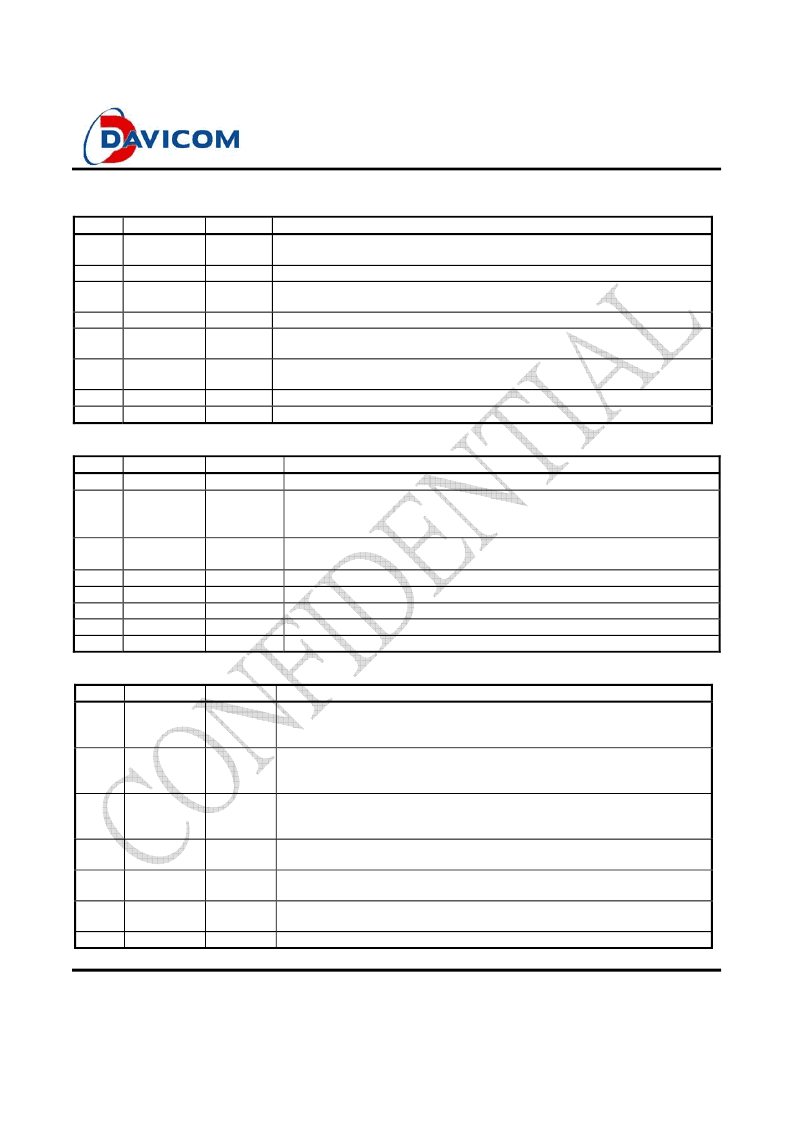

6.2 Network Status Register (01H)

Bit

Name

Default

Description

7

SPEED

X,RO

Media Speed 0:100Mbps 1:10Mbps, when Internal PHY is used. This bit has no

meaning when LINKST=0

Link Status 0:link failed 1:link OK,

Wakeup Event Status. Clears by read or write 1 (work in 8-bit mode)

This bit will not be affected after software reset

Reserved

TX Packet 2 Complete Status. Clears by read or write 1

Transmit completion of packet index 2

TX Packet 1 Complete status. Clears by read or write 1

Transmit completion of packet index 1

PHS0,RO RX FIFO Overflow

0,RO

Reserved

6

LINKST

X,RO

P0,

RW/C1

0,RO

PHS0,

RW/C1

PHS0,

RW/C1

5

WAKEST

4

RESERVED

3

TX2END

2

TX1END

1

0

RXOV

RESERVED

6.3 TX Control Register (02H)

Bit

Name

7

RESERVED

Default

0,RO

Description

Reserved

Transmit Jabber Disable

When set, the transmit Jabber Timer (2048 bytes) is disabled. Otherwise it is

Enable

Excessive Collision Mode Control : 0:aborts this packet when excessive collision

counts more than 15, 1: still tries to transmit this packet

PAD Appends Disable for Packet Index 2

CRC Appends Disable for Packet Index 2

PAD Appends Disable for Packet Index 1

CRC Appends Disable for Packet Index 1

TX Request. Auto clears after sending completely

6

TJDIS

PHS0,RW

5

EXCECM

PHS0,RW

4

3

2

1

0

PAD_DIS2

CRC_DIS2

PAD_DIS1

CRC_DIS1

TXREQ

PHS0,RW

PHS0,RW

PHS0,RW

PHS0,RW

PHS0,RW

6.4 TX Status Register I ( 03H ) for packet index I

Bit

Name

Default

Description

7

TJTO

PHS0,RO

Transmit Jabber Time Out

It is set to indicate that the transmitted frame is truncated due to more than 2048

bytes are transmitted

Loss of Carrier

It is set to indicate the loss of carrier during the frame transmission. It is not valid in

internal loopback mode

No Carrier

It is set to indicate that there is no carrier signal during the frame transmission. It is

not valid in internal loopback mode

Late Collision

It is set when a collision occurs after the collision window of 64 bytes

Collision Packet

It is set to indicate that the collision occurs during transmission

Excessive Collision

It is set to indicate that the transmission is aborted due to 16 excessive collisions

Reserved

6

LC

PHS0,RO

5

NC

PHS0,RO

4

LC

PHS0,RO

3

COL

PHS0,RO

2

EC

PHS0,RO

1:0

RESERVED

0,RO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9000AEP | Ethernet Controller with General Processor Interface |

| DM9000 | ISA TO ETHERNET MAC CONTROLLER WITH INTEGRATED 10/100 PHY |

| DM9000E | ISA TO ETHERNET MAC CONTROLLER WITH INTEGRATED 10/100 PHY |

| DM9006CJ | Gate Expander |

| DM9006CN | Gate Expander |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9000AEP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:網(wǎng)絡接口電路 |

| DM9000B | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Ethernet Controller With General Processor Interface |

| DM9000B_12 | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Ethernet Controller With General Processor Interface |

| DM9000BE | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Ethernet Controller with General Processor Interface |

| DM9000BEP | 制造商:DAVICOM 功能描述:IC ENET CNTRL 10/100M PHY 48LQFP 制造商:DAVICOM 功能描述:IC, ENET CNTRL, 10/100M PHY, 48LQFP 制造商:DAVICOM 功能描述:IC, ENET CNTRL, 10/100M PHY, 48LQFP; Data Rate:100Mbps; Ethernet Type:IEEE 802.3u; Supply Voltage Min:3.135V; Supply Voltage Max:3.465V; Digital IC Case Style:LQFP; No. of Pins:48; Interface Type:MII; Operating Temperature Min:0C; ;RoHS Compliant: Yes |

發(fā)布緊急采購,3分鐘左右您將得到回復。