- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376802 > DM9081 (Electronic Theatre Controls, Inc.) 10BASE-T Hub Controller PDF資料下載

參數(shù)資料

| 型號: | DM9081 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 10BASE-T Hub Controller |

| 中文描述: | 10Base - T集線器控制器 |

| 文件頁數(shù): | 4/22頁 |

| 文件大小: | 188K |

| 代理商: | DM9081 |

DM9081

4

Final

Version: DM9081-DS-F01

April 22, 1997

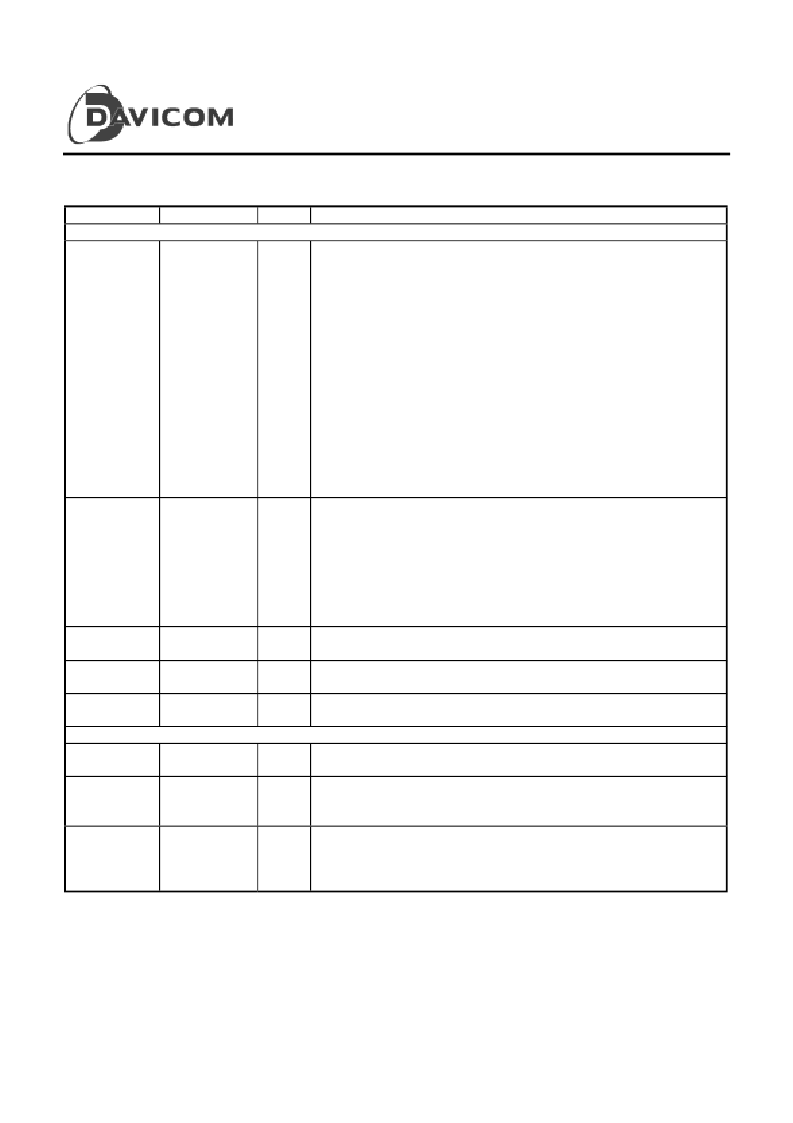

Pin Description

Pin No.

Transceiver

100, 1

99, 2

34, 31

33, 32

39, 36

38, 37

44, 41

43, 42

49, 46

48, 47

84, 87

85, 86

89, 92

90, 91

94, 97

95, 96

52, 51

54, 53

56, 55

58, 57

60, 59

62, 61

64, 63

66, 65

70, 69

76, 75

72, 71

78, 77

74, 73

80, 79

Expansion Port

24

Pin Name

I/O

Description

DTPO3+/-

TPO3+/-

TPO4+/-

DTPO4+/-

TPO5+/-

DTPO5+/-

TPO6+/-

DTPO6+/-

TPO7+/-

DTPO7+/-

TPO0+/-

DTPO0+/-

TPO1+/-

DTPO1+/-

TPO2+/-

DTPO2+/-

RXD7+/-

RXD6+/-

RXD5+/-

RXD4+/-

RXD3+/-

RXD2+/-

RXD1+/-

RXD0+/-

TXP1, TXN1

TXP2, TXN2

RXP1, RXN1

RXP2, RXN2

CDP1, CDN1

CDP2, CDN2

O

TP Driver Outputs

. The TPO+/- output generate 10Mbits/s Manchester-

encoded data. The DTPO+/- outputs are one-half bit time delayed and

inverted with respect to TPO+/-. These four outputs provide the TP drivers

with pre-distortion capability

I

10BASE-T Port Different Data Receivers

O

AUI Port Different Data Drivers

. The outputs are source followers that

require a 270

pull-down resistor

AUI Port Differential Receive Input Pair

I

I

AUI Port Different Collision Input Pair

EXPOUT#

O

The assertion of this signal indicates that DM9081 is transmitting data on

DAT pins. It is active low

The assertion of this signal indicates that DM9081 is receiving data on

DAT pins. The receiving data will be broadcast to the other ports. It is

active low and is internally pulled high with a 100K

resistor

The DAT pins of all DM9081 chips are inter-connected. The active

DM9081 drives DAT with repeated data or jam signals in NRZ format.

The inactive DM9081 receives the repeated data or jam signals from the

DAT pin

22

EXPIN#

I

23

DAT

I/O,Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9081F | 10BASE-T Hub Controller |

| DM9095 | Twisted-Pair Medium Attachment Unit |

| DM9095L | Twisted-Pair Medium Attachment Unit |

| DM9102D | SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

| DM9102DE | SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9081_01 | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10BASE-T Hub Controller |

| DM9081F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10BASE-T Hub Controller |

| DM9081FP | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10BASE-T Hub Controller |

| DM9093 WAF | 制造商:Texas Instruments 功能描述: |

| DM9093J/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:J-K-Type Flip-Flop |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。