- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376803 > DM9322 PDF資料下載

參數(shù)資料

| 型號(hào): | DM9322 |

| 文件頁(yè)數(shù): | 75/158頁(yè) |

| 文件大小: | 2668K |

| 代理商: | DM9322 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)當(dāng)前第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)

Switching Characteristics

V

CC

e a

5.0V, T

A

e a

25

§

C (See Section 1 for waveforms and load configurations)

C

L

e

15 pF

Symbol

Parameter

9338 (MIL)

DM9338 (COM)

Units

Min

Max

Min

Max

t

PLH

t

PHL

Propagation Delay

B

n

or C

n

to Z

n

40

35

13

18

40

35

ns

t

PLH

t

PHL

Propagation Delay

D

A

to Z

n

45

50

25

25

45

50

ns

t

PLH

t

PHL

Propagation Delay

CP to Z

n

35

30

18

13

35

30

ns

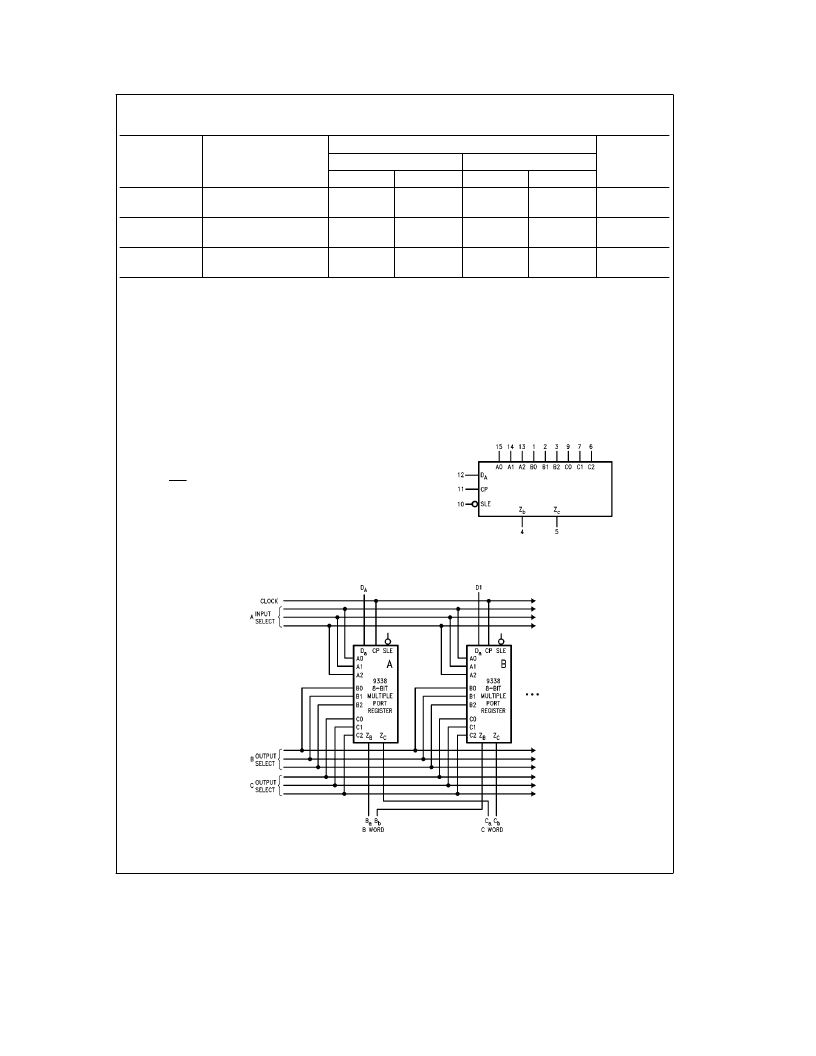

Functional Description

The 9338 8-bit multiple port register can be considered a 1-

bit slice of eight high speed working registers. Data can be

written into any one and read from any two of the eight

locations simultaneously. Master/slave operation eliminates

all race problems associated with simultaneous read/write

activity from the same location. When the clock input (CP) is

LOW data applied to the data input line (D

A

) enters the

selected master. This selection is accomplished by coding

the three write input select lines (A0–A2) appropriately.

Data is stored synchronously with the rising edge of the

clock pulse.

The information for each of the two slaved (output) latches

is selected by two sets of read address inputs (B0–B2 and

C0–C2). The information enters the slave while the clock is

HIGH and is stored while the clock is LOW. If Slave Enable

is LOW (SLE), the slave latches are continuously enabled.

The signals are available on the output pins (Z

B

and Z

C

).

The input bit selection and the two output bit selections can

be accomplished independently or simultaneously. The data

flows into the device, is demultiplexed according to the state

of the write address lines and is clocked into the selected

latch. The eight latches function as masters and store the

input data. The two output latches are slaves and hold the

data during the read operation. The state of each slave is

determined by the state of the master selected by its associ-

ated set of read address inputs.

The method of parallel expansion is shown inFigure a. One

9338 is needed for each bit of the required word length. The

read and write input lines should be connected in common

on all of the devices. This register configuration provides

two words of n-bits each at one time, where n devices are

connected in parallel.

Logic Symbol

TL/F/9794–2

V

CC

e

Pin 16

GND

e

Pin 8

TL/F/9794–4

FIGURE a. Parallel Expansion

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9368 | 7-Segment Decoder/Driver/Latch with Constant Current Source Outputs |

| DM9638N | 7-Segment Decoder/Driver/Latch with Constant Current Source Outputs |

| DM9368N | LED Display Driver |

| DM9370 | 7-Segment Decoder/Driver/Latch with Open-Collector Outputs(集電極開(kāi)路輸出的7段譯碼器/驅(qū)動(dòng)器/鎖存器) |

| DM9370N | Decoder/Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9322 WAF | 制造商:Texas Instruments 功能描述: |

| DM9322J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-Input Digital Multiplexer |

| DM9322J/883 | 制造商:Rochester Electronics LLC 功能描述: 制造商:National Semiconductor 功能描述:9322 制造商:Texas Instruments 功能描述: |

| DM9322J883 | 制造商:National Semiconductor 功能描述:9322 |

| DM9322N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2-Input Digital Multiplexer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。