- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9559 > DS2181AQN (Maxim Integrated Products)IC TXRX CEPT PRIM RATE IN 44PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | DS2181AQN |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 6/32頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC TXRX CEPT PRIM RATE IN 44PLCC |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 26 |

| 類型: | 收發(fā)器 |

| 驅(qū)動(dòng)器/接收器數(shù): | 1/1 |

| 規(guī)程: | CEPT |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 44-PLCC(16.59x16.59) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

DS2181A

14 of 32

Bits 4 through 8 of timeslot 0 in non-align frames are reserved for national use. When TCR.3 = 1, the

transmitted national bits are sourced from register locations TINR.4 through TINR.0. If TCR.3 = 0, the

national bits are sampled at TIND during bit times 4 through 8 of timeslot 0 in non-align frames.

Reserved bit positions in the TINR must be set to 0 when written; those bits can be 0 or 1 when read.

TXR: TRANSMIT EXTRA REGISTER Figure 10

(MSB)

(LSB)

-

XB1

TDMA

XB2

XB3

SYMBOL

POSITION

NAME AND DESCRIPTION

-

TXR.7

Reserved; must be 0 for proper operation.

-

TXR.6

Reserved; must be 0 for proper operation.

-

TXR.5

Reserved; must be 0 for proper operation.

-

TXR.4

Reserved; must be 0 for proper operation.

XB1

TXR.3

Extra Bit 1

TDMA

TXR.2

Transmit Distant Multiframe Alarm

0 = Normal operation; bit 6 of timeslot 16 in frame 0 clear.

1 = Alarm condition; bit 6 of timeslot 16 in frame 0 set.

XB2

TXR.1

Extra Bit 2

XB3

TXR.0

Extra Bit 3

TRANSMIT EXTRA DATA

In the CAS mode, timeslot 16 of frame 0 contains the multiframe alignment pattern, extra bits and the

distant multiframe alarm. When CAS is enabled (TCR.5 = 0), the extra bits are sourced from TXR.0,

TXR.1 and TXR.3 (TCR.2 = 1) or the extra bits are sampled externally at TXD during the extra bit time

(TCR.2 = 0). The extra bits, alignment pattern and alarm signal are not utilized in the CCS mode (TCR.5

= 1); input TSER overwrites all timeslot 16 bit positions.

Reserved bit positions in the TXR must be set to 0 when written; those bits can be 0 or 1 when read.

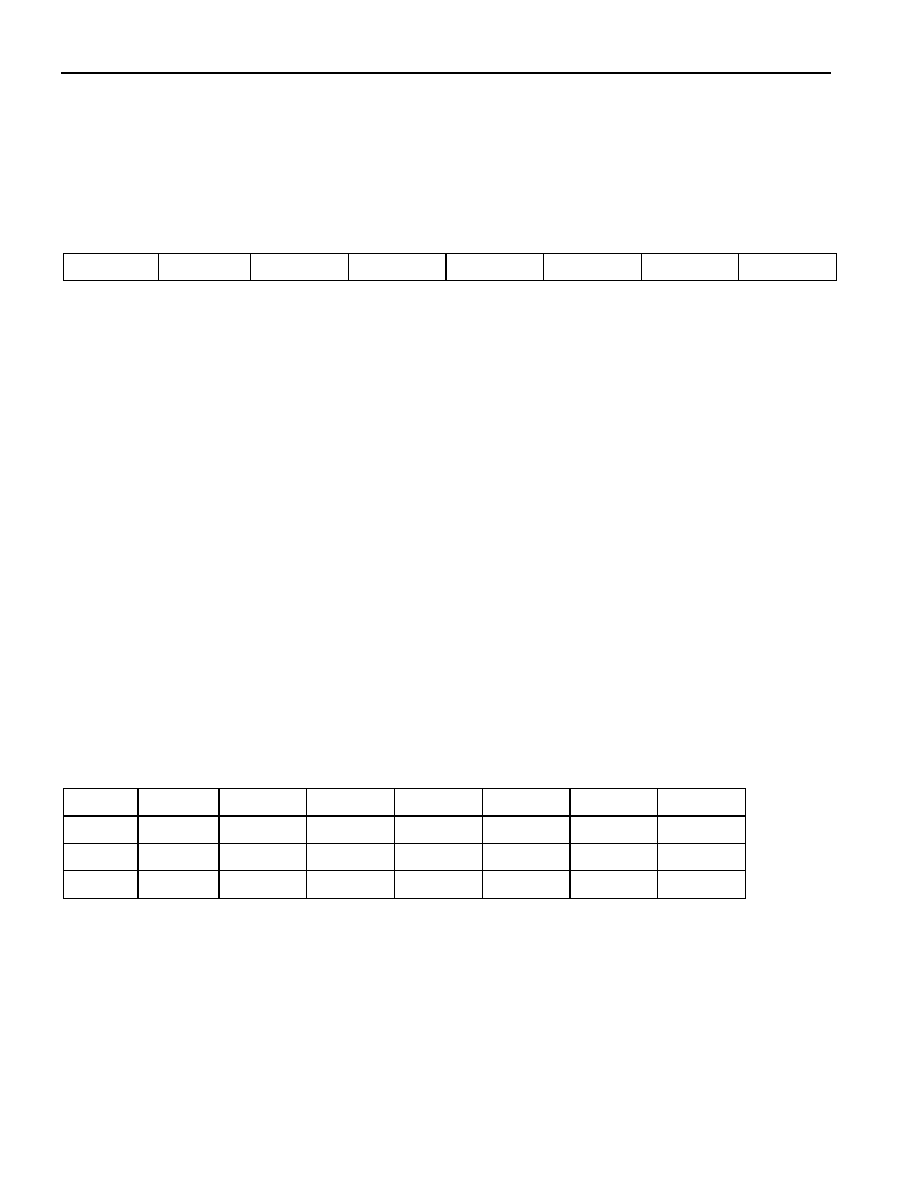

TIR1 - TIR4: TRANSMIT IDLE REGISTERS Figure 11

(MSB)

(LSB)

TS7

TS6

TS5

TS4

TS3

TS2

TS1

TS0

1

TIR1

TS15

TS14

TS13

TS12

TS11

TS10

TS9

TS8

TIR2

TS23

TS22

TS21

TS20

TS19

TS18

TS17

TS16

1

TIR3

TS31

TS30

TS29

TS28

TS27

TS26

TS25

TS024

TIR4

SYMBOL

POSITION

NAME AND DESCRIPTION

TS31

TIR4.7

Transmit Idle Registers

TS0

TIR1.0

Each of these bit positions represents a timeslot in the outgoing

stream at TPOS and TNEG; when set, the contents of that timeslot

are forced to idle code (11010101).

NOTE:

1. TS0 and TS16 are not affected by the idle register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-B6T-MY-S | CONVERTER MOD DC/DC 6.5V 50W |

| VI-26R-MY-S | CONVERTER MOD DC/DC 7.5V 50W |

| DS275S | IC TXRX LINE-PWR RS232 8-SOIC |

| VI-26M-MY-S | CONVERTER MOD DC/DC 10V 50W |

| MS27473E18B11PB | CONN PLUG 11POS STRAIGHT W/PINS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2181AQN/T&R | 制造商:Maxim Integrated Products 功能描述:CEPT TRANSCEIVER-PLCC-IND-TRL - Tape and Reel 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:IC TXRX CEPT PRIM RATE IN 44PLCC 制造商:Maxim Integrated Products 功能描述:Network Controller & Processor ICs CEPT Primary Rate Transceiver |

| DS2181AQN/T&R+ | 制造商:Maxim Integrated Products 功能描述:CEPT TRANSEIVER PLCC IND TRL LF - Tape and Reel |

| DS2181AQN/T&R | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2181AQN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC CEPT Primary Rate Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2181AQN+T&R | 制造商:Maxim Integrated Products 功能描述: 制造商:Maxim Integrated Products 功能描述:CEPT TRNSCVR 1TX 1RX 44PLCC - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC TXRX CEPT PRIMARY RATE 44PLCC 制造商:Maxim Integrated Products 功能描述:Network Controller & Processor ICs CEPT Primary Rate Transceiver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。