- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10985 > DS2187+ (Maxim Integrated Products)IC RECEIVE LINE INTERFACE 18-DIP PDF資料下載

參數(shù)資料

| 型號: | DS2187+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 3/10頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC RECEIVE LINE INTERFACE 18-DIP |

| 標(biāo)準(zhǔn)包裝: | 20 |

| 功能: | 接收線路接口 |

| 接口: | T1 |

| 電路數(shù): | 1 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 電流 - 電源: | 18mA |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 通孔 |

| 封裝/外殼: | 18-DIP(0.300",7.62mm) |

| 供應(yīng)商設(shè)備封裝: | 18-PDIP |

| 包裝: | 管件 |

| 包括: | AMI / B8ZS / HDB3 編碼信號解碼器 |

DS2187

2 of 10

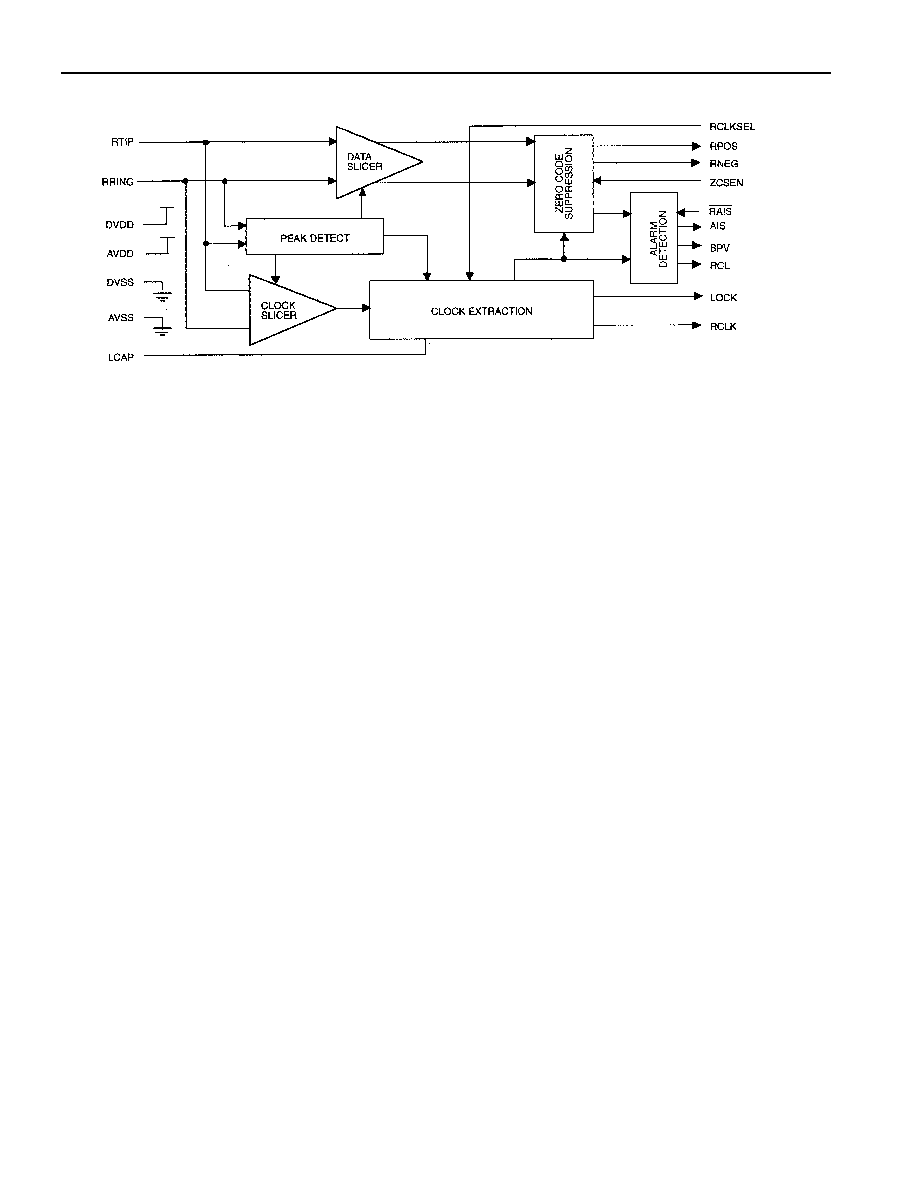

DS2187 BLOCK DIAGRAM Figure 1

LINE INPUT

Input signals are coupled to the DS2187 via a 1:2 center-tapped transformer as shown in Figure 2. For T1

applications, R1 and R2 must be 200 ohms in order to properly terminate the line at 100 ohms. R1 and R2

are set at 150 or 240 ohms for CEPT applications. Special internal circuitry of the RTIP and RRING

inputs permits negative signal excursions below VSS, which will occur in the circuit in Figure 2.

PEAK DETECTOR AND SLICERS

Signal pulses present at RTIP and RRING are sampled by an internal peak detect circuit. The clock and

data slicer threshold are set for 50% of the sampled peak voltage.

Peak input levels at RRIP and RRING must exceed 0.6 volts to establish minimum slicer thresholds.

Signals below this level will cause RCL to transition high after 192 bit times.

CLOCK EXTRACTION

The DS2187 utilizes both frequency locked (FLL) and digital phase locked (DPLL) loops to recover data

and clock from the incoming AMI signal. T1 applications utilize a 18.528 MHz clock divided by either

11, 12, or 13 to match the phase of the incoming jittered line signal. This technique affords exceptional

jitter tracking which enables the DS2187 to meet the latest AT&T TR 62411 and ECSA jitter

specifications. A 24.576 MHz clock divided by 11, 12, or 13 provides jitter tracking in the CEPT mode.

The DPLL output is buffered and presented at RCLK. An on-chip, laser-trimmed, voltage-controlled

oscillator (VCO) provides the precision 18.528 MHz and 24.576 MHz frequency sources utilized in the

FLL. The FLL is a high-Q circuit which tracks the average frequency of the incoming signal, minimizing

the effect of the DPLL on output jitter.

During the acquisition time or if RCL goes high, the LOCK pin will go low to indicate a loss of

synchronization to the line signal. Once this pin goes high, the FLL has achieved frequency lock and

valid data is present at the RPOS and RNEG outputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21Q59L | IC TXRX E1 QUAD 3.3V 100-LQFP |

| VI-B5Z-IX-F2 | CONVERTER MOD DC/DC 2V 30W |

| VI-B5Y-IY-F3 | CONVERTER MOD DC/DC 3.3V 33W |

| VI-B5Y-IX-F1 | CONVERTER MOD DC/DC 3.3V 49.5W |

| VI-B5Y-IW-F4 | CONVERTER MOD DC/DC 3.3V 66W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2187+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Receive Line Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2187S | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Receive Line Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2187S/T&R | 制造商:Maxim Integrated Products 功能描述:IC RECEIVE LINE INTERFACE 20SOIC |

| DS2187S/T&R | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Receive Line Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2187S+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Receive Line Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。