- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376976 > DS3251N Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs PDF資料下載

參數(shù)資料

| 型號: | DS3251N |

| 英文描述: | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| 中文描述: | 單/雙/三/四DS3/E3/STS-1柳斯 |

| 文件頁數(shù): | 10/71頁 |

| 文件大小: | 925K |

| 代理商: | DS3251N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

DS3251/DS3252/DS3253/DS3254

10 of 71

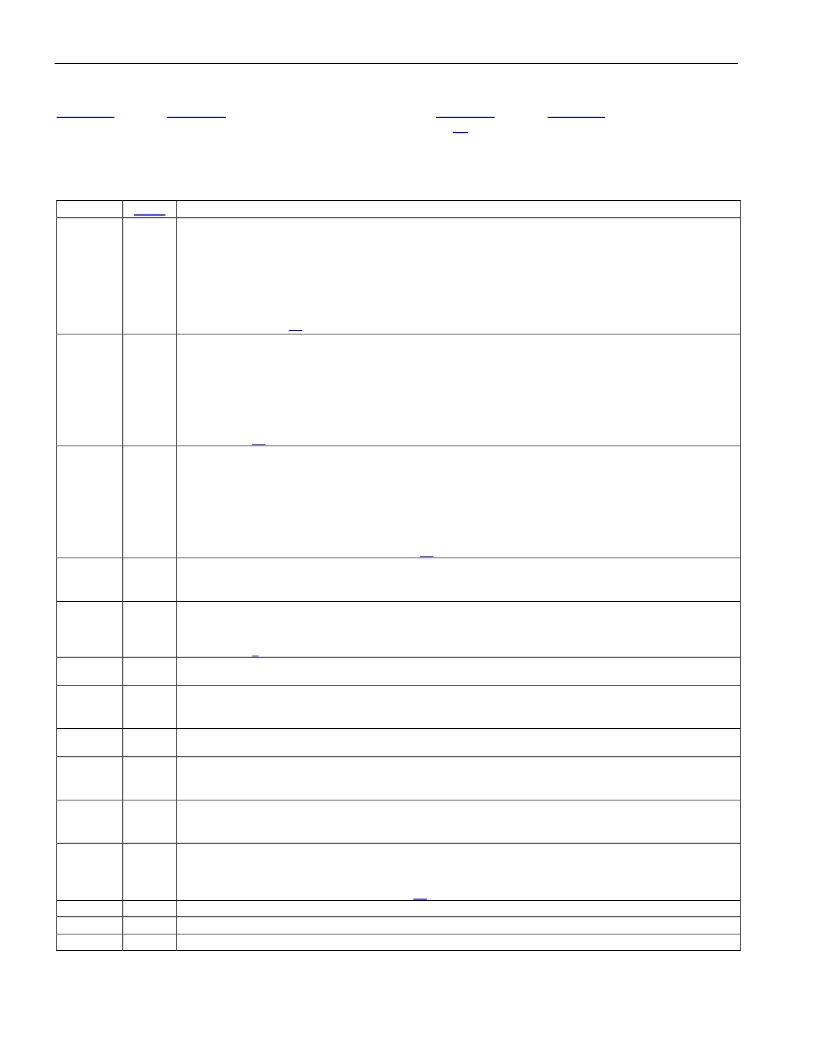

6. PIN DESCRIPTIONS

Table 6-A

through

Table 6-C

list the pins that are always active.

Table 6-D

through

Table 6-F

list the additional pins

that active in each of the three control interface modes. Section

18

shows pin assignments for all three control

interface modes.

Table 6-A. Global Pin Descriptions

Note:

These pins are always active.

NAME

TYPE

T3 Master Clock.

If a clock is applied to T3MCLK, it must be transmission-quality ( 20ppm, low jitter).

When present, the T3MCLK signal serves as the DS3 master clock for the CDRs and jitter attenuators

of all LIUs configured for DS3 operation. If T3MCLK is held low, the clock adapter block synthesizes the

DS3 master clock from the clock applied to E3MCLK (first choice) or the clock applied to STMCLK

(second choice). If T3MCLK is held high, each LIU in DS3 mode uses its TCLK signal as its master

clock. If T3MCLK is held low but E3MCLK and STMCLK are not toggling, then each LIU in DS3 mode

uses its TCLK signal as its master clock. Pin is input-only in Hardware mode, input/output in CPU Bus

mode. See Section

12

for more information.

E3 Master Clock.

If a clock is applied to E3MCLK, it must be transmission-quality ( 20ppm, low jitter).

When present, the E3MCLK signal serves as the E3 master clock for the CDRs and jitter attenuators of

all LIUs configured for E3 operation. If E3MCLK is held low, the clock adapter block synthesizes the E3

master clock from the clock applied to T3MCLK (first choice) or the clock applied to STMCLK (second

choice). If E3MCLK is held high, each LIU in E3 mode uses its TCLK signal as its master clock. If

E3MCLK is held low but T3MCLK and STMCLK are not toggling, then each LIU in E3 mode uses its

TCLK signal as its master clock. Pin is input-only in Hardware mode, input/output in CPU Bus mode.

See Section

12

for more information.

STS-1 Master Clock.

If a clock is applied to STMCLK, it must be transmission-quality ( 20ppm, low

jitter). When present, the STMCLK signal serves as the STS-1 master clock for the CDRs and jitter

attenuators of all LIUs configured for STS-1 operation. If STMCLK is held low, the clock adapter block

synthesizes the STS-1 master clock from the clock applied to T3MCLK (first choice) or the clock

applied to E3MCLK (second choice). If STMCLK is held high, each LIU in STS-1 mode uses its TCLK

signal as its master clock. If STMCLK is held low but T3MCLK and E3MCLK are not toggling, then each

LIU in STS-1 mode uses its TCLK signal as its master clock. Pin is input-only in Hardware mode,

input/output in CPU Bus mode. See Section

12

for more information.

High-Z Enable Input (Active Low, Open Drain, Internal 10k Pullup to V

DD

)

0 = tri-state all output pins (Note that the

JTRST

pin must be low.)

1 = normal operation

Hardware Mode Select

0 = CPU bus mode

1 = Hardware mode

See Section

5

for details.

JTAG IEEE 1149.1 Test Serial Clock.

JTCLK shifts data into JTDI on the rising edge and out of JTDO

on the falling edge. If boundary scan is not used, JTCLK should be pulled high.

JTAG IEEE 1149.1 Test Serial-Data Input (Internal 10k Pullup).

Test instructions and data are

clocked in on this pin on the rising edge of JTCLK. If boundary scan is not used, JTDI should be left

unconnected or pulled high.

JTAG IEEE 1149.1 Test Serial-Data Output.

Test instructions and data are clocked out on this pin on

the falling edge of JTCLK.

JTAG IEEE 1149.1 Test Reset (Internal 10k Pullup to V

DD

).

This pin is used to asynchronously

reset the test access port (TAP) controller. If boundary scan is not used,

JTRST

can be held low or

high.

JTAG IEEE 1149.1 Test Mode Select (Internal 10k Pullup to V

DD

).

This pin is sampled on the rising

edge of JTCLK and is used to place the port into the various defined IEEE 1149.1 states. If boundary

scan is not used, JTMS should be left unconnected or pulled high.

Reset Input (Active Low, Open Drain, Internal 10k Pullup to V

DD

).

When this global asynchronous

reset is pulled low, the internal circuitry is reset and the internal registers (CPU bus mode) are forced to

their default values. The device is held in reset as long as

RST

is low.

RST

should be held low for at

least two master clock cycles. See Section

13

for more information.

TEST

I

PU

Factory Test Pin.

Leave unconnected or wire high for normal operation.

V

DD

P

Positive Supply.

3.3V 5%. All V

DD

signals should be wired together.

V

SS

P

Ground Reference.

All V

SS

signals should be wired together.

FUNCTION

T3MCLK

I/O

E3MCLK

I/O

STMCLK

I/O

HIZ

I

PU

HW

I

JTCLK

I

JTDI

I

PU

JTDO

O

JTRST

I

PU

JTMS

I

PU

RST

I

PU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3252 | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3252N | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3253 | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3253N | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

| DS3254 | Single/Dual/Triple/Quad DS3/E3/STS-1 LIUs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3251N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3251NA3 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252A3 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。