- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄171234 > DSP56F802TA60E (飛思卡爾半導(dǎo)體(中國)有限公司) 16-bit Digital Signal Controllers PDF資料下載

參數(shù)資料

| 型號: | DSP56F802TA60E |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 16-bit Digital Signal Controllers |

| 中文描述: | 16位數(shù)字信號控制器 |

| 文件頁數(shù): | 16/40頁 |

| 文件大小: | 2472K |

| 代理商: | DSP56F802TA60E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

Clock Operation

56F802 Technical Data, Rev. 7

Freescale Semiconductor

23

3.5 Clock Operation

The 56F802 device clock is derived from an on-chip relaxation oscillator. The internal PLL generates a

master reference frequency that determines the speed at which chip operations occur.

The PRECS bit in the PLLCR (phase-locked loop control register) word (bit 2) must be set to 0 for internal

oscillator use.

3.5.1

Use of On-Chip Relaxation Oscillator

The 56F802 internal relaxation oscillator provides the chip clock without the need for an external crystal

or ceramic resonator. The frequency output of this internal oscillator can be corrected by adjusting the 8-bit

IOSCTL (internal oscillator control) register. Each bit added or deleted changes the output frequency of

the oscillator allowing incremental adjustment until the desired frequency is achieved. Figures 9 and 10

show the typical characteristics of the 56F802 relaxation oscillator with respect to temperature and trim

value.

During factory production test, an oscillator calibration procedure is executed which determines an

optimum trim value for a given device (8MHz at 25oC). This optimum trim value is then stored at address

$103F in the Data Flash Information Block and recalled during a trim routine in the boot sequence

(executed after power-up and RESET). This trim routine automatically sets the oscillator frequency by

programming the IOSCTL register with the optimum trim value.

Due to the inherent frequency tolerances required for SCI communication, changing the factory-trimmed

oscillator frequency is not recommended. If modification of the Boot Flash contents are required, code

must be included which retrieves the optimum trim value (from address $103F in the Data Flash

Information Block) and writes it to the IOSCTL register. Note that the IFREN bit in the Data Flash control

register must be set in order to read the Data Flash Information Block.

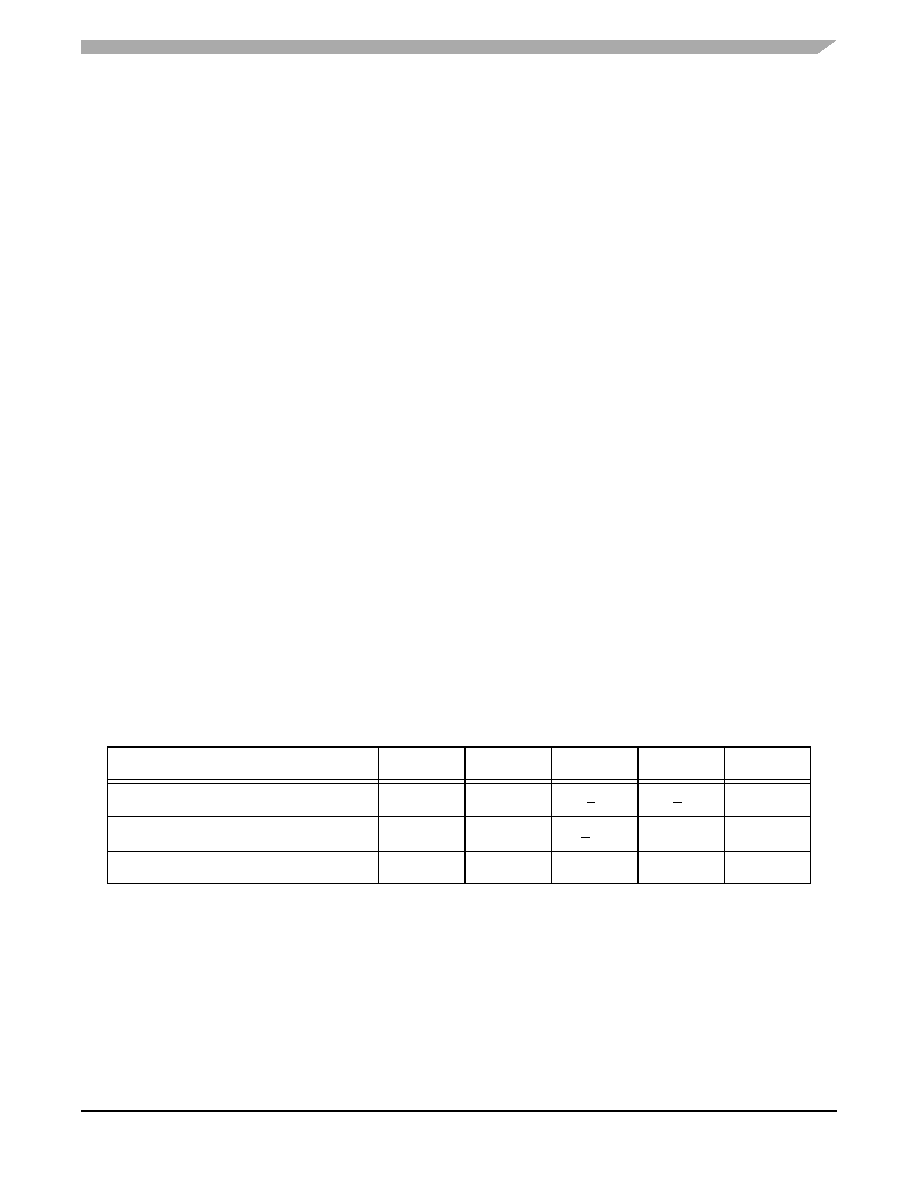

Table 3-8 Relaxation Oscillator Characteristics

Operating Conditions: VSS = VSSA = 0 V, VDD = VDDA = 3.0–3.6 V, TA = –40° to +85°C

Characteristic

Symbol

Min

Typ

Max

Unit

Frequency Accuracy1

1. Over full temperature range.

f

—

+2

+5

%

Frequency Drift over Temp

f/t

—

+0.1

—

%/oC

Frequency Drift over Supply

f/V

—

0.1

—

%/V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56F802TA80 | 16-bit Digital Signal Controllers |

| DSP56F802TA80E | 16-bit Digital Signal Controllers |

| DSP56F802 | Digital Switched-Mode Power Supply (SMPS) |

| DSP56F803 | Digital Switched-Mode Power Supply (SMPS) |

| DSPA56371 | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56F802TA80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| DSP56F802TA80E | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CONTROLLER RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| DSP56F803 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Digital Switched-Mode Power Supply (SMPS) |

| DSP56F803BU80 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 80Mhz/ 40MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| DSP56F803BU80E | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 80Mhz/40 MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。