- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4317 > EP1S80F1020C6N (Altera)IC STRATIX FPGA 80K LE 1020-FBGA PDF資料下載

參數(shù)資料

| 型號: | EP1S80F1020C6N |

| 廠商: | Altera |

| 文件頁數(shù): | 471/864頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX FPGA 80K LE 1020-FBGA |

| 產(chǎn)品培訓模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 產(chǎn)品變化通告: | Package Height Change 03/March/2008 |

| 標準包裝: | 8 |

| 系列: | Stratix® |

| LAB/CLB數(shù): | 7904 |

| 邏輯元件/單元數(shù): | 79040 |

| RAM 位總計: | 7427520 |

| 輸入/輸出數(shù): | 773 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 1020-BBGA |

| 供應商設備封裝: | 1020-FBGA(33x33) |

5–50

Altera Corporation

Stratix Device Handbook, Volume 2

July 2005

Board Design Consideration

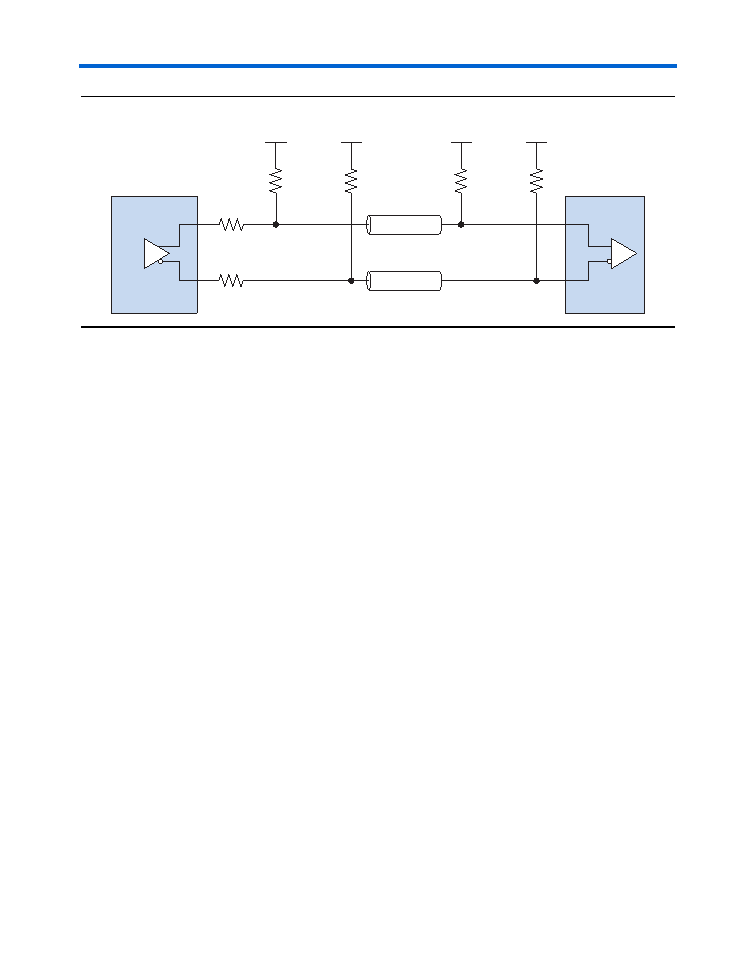

Figure 5–39. Differential SSTL-2 Class II Termination

Board Design

Consideration

This section is a brief explanation of how to get the optimal performance

from the Stratix high-speed I/O block and ensure first-time success in

implementing a functional design with optimal signal quality. For more

information on detailed board layout recommendation and I/O pin

terminations see AN 224: High-Speed Board Layout Guidelines.

You must consider the critical issues of controlled impedance of traces

and connectors, differential routing, and termination techniques to get

the best performance from the IC. For more information, use this chapter

and the Stratix Device Family Data Sheet section of the Stratix Device

Handbook, Volume 1.

The Stratix high-speed module generates signals that travel over the

media at frequencies as high as 840 Mbps. Board designers should use the

following general guidelines:

■

Baseboard designs on controlled differential impedance. Calculate

and compare all parameters such as trace width, trace thickness, and

the distance between two differential traces.

■

Place external reference resistors as close to receiver input pins as

possible.

■

Use surface mount components.

■

Avoid 90° or 45° corners.

■

Use high-performance connectors such as HS-3 connectors for

backplane designs. High-performance connectors are provided by

Teradyne Corp (www.teradyne.com) or Tyco International Ltd.

(www.tyco.com).

■

Design backplane and card traces so that trace impedance matches

the connector’s and/or the termination’s impedance.

■

Keep equal number of vias for both signal traces.

Differential

Transmitter

Differential

Receiver

Z0 = 50 Ω

50

Ω

50

Ω

Z0 = 50 Ω

VTT = 1.25 V

50

Ω

50

Ω

VTT = 1.25 V

25

Ω

25

Ω

相關PDF資料 |

PDF描述 |

|---|---|

| EP4SGX360HF35C4 | IC STRATIX IV FPGA 360K 1152FBGA |

| AMM25DTMN | CONN EDGECARD 50POS R/A .156 SLD |

| AMM25DTMH | CONN EDGECARD 50POS R/A .156 SLD |

| 24AA024HT-I/MS | IC EEPROM 2KBIT 400KHZ 8MSOP |

| EP4SGX230HF35I4 | IC STRATIX IV FPGA 230K 1152FBGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP1S80F1020C7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix I 7904 LABs 773 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1020C7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix I 7904 LABs 773 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1020I7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix I 7904 LABs 773 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1020I7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix I 7904 LABs 773 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1S80F1508C5 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Stratix I 7904 LABs 1203 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。