- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄4337 > EP2AGX190EF29I5N (Altera)IC ARRIA II GX FPGA 190K 780FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP2AGX190EF29I5N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 84/90頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ARRIA II GX FPGA 190K 780FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 4 |

| 系列: | Arria II GX |

| LAB/CLB數(shù): | 7612 |

| 邏輯元件/單元數(shù): | 181165 |

| RAM 位總計(jì): | 10177536 |

| 輸入/輸出數(shù): | 372 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 780-BBGA |

| 供應(yīng)商設(shè)備封裝: | 780-FBGA(29x29) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)當(dāng)前第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)

Chapter 1: Device Datasheet for Arria II Devices

1–77

Document Revision History

December 2013

Altera Corporation

Document Revision History

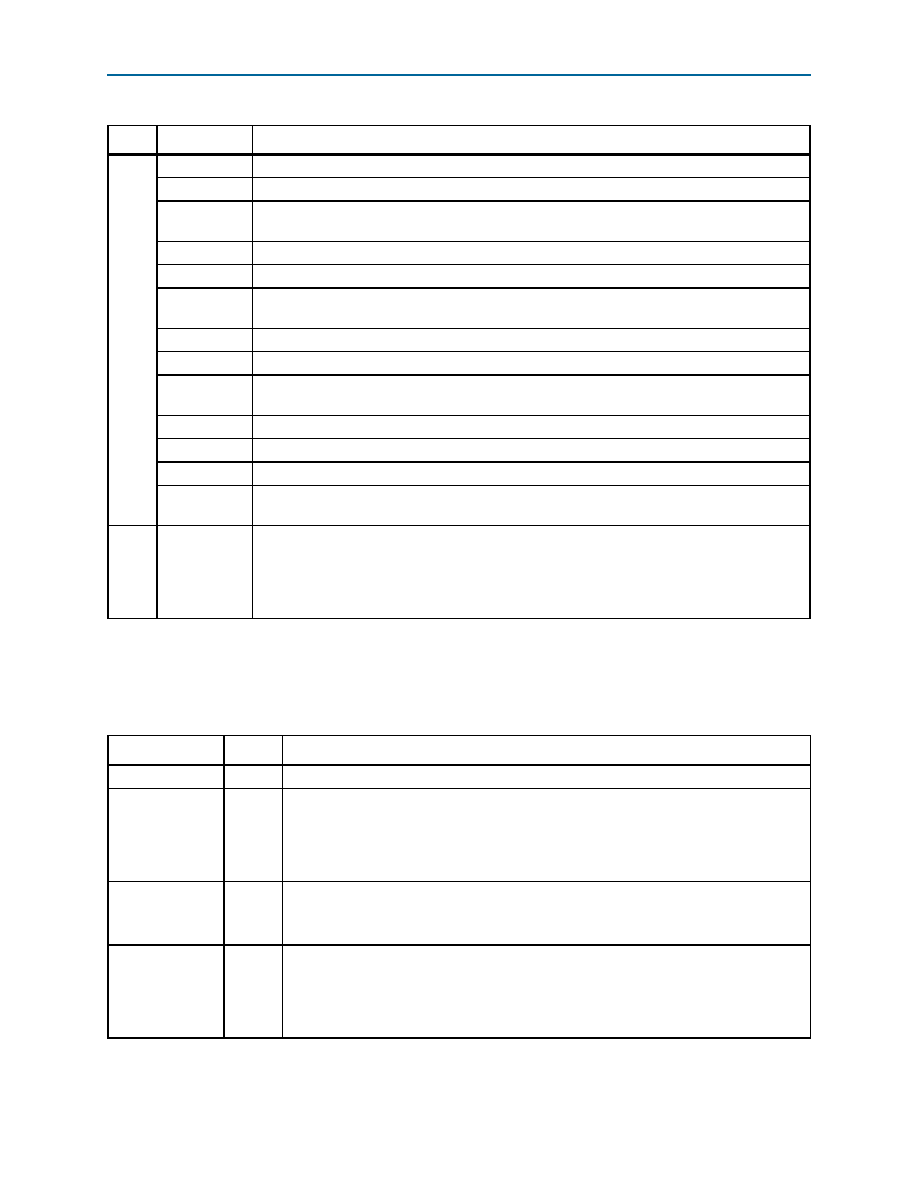

Table 1–69 lists the revision history for this chapter.

U,

V

VCM(DC)

DC common mode input voltage.

VICM

Input common mode voltage: The common mode of the differential signal at the receiver.

VID

Input differential voltage swing: The difference in voltage between the positive and

complementary conductors of a differential transmission at the receiver.

VDIF(AC)

AC differential input voltage: Minimum AC input differential voltage required for switching.

VDIF(DC)

DC differential input voltage: Minimum DC input differential voltage required for switching.

VIH

Voltage input high: The minimum positive voltage applied to the input which is accepted by the

device as a logic high.

VIH(AC)

High-level AC input voltage.

VIH(DC)

High-level DC input voltage.

VIL

Voltage input low: The maximum positive voltage applied to the input which is accepted by the

device as a logic low.

VIL(AC)

Low-level AC input voltage.

VIL(DC)

Low-level DC input voltage.

VOCM

Output common mode voltage: The common mode of the differential signal at the transmitter.

VOD

Output differential voltage swing: The difference in voltage between the positive and

complementary conductors of a differential transmission at the transmitter.

W,

X,

Y,

Z

W

High-speed I/O block: The clock boost factor.

Table 1–68. Glossary (Part 4 of 4)

Letter

Subject

Definitions

Table 1–69. Document Revision History (Part 1 of 2)

Date

Version

Changes

December 2013

4.4

Updated Table 1–34 and Table 1–35.

July 2012

4.3

■ Updated the VCCH_GXBL/R operating conditions in Table 1–6.

■ Finalized Arria II GZ information in Table 1–20.

■ Added BLVDS specification in Table 1–32 and Table 1–33.

■ Updated input and output waveforms in Table 1–68.

December 2011

4.2

■ Updated Table 1–32, Table 1–33, Table 1–34, Table 1–35, Table 1–40, Table 1–41,

Table 1–54, and Table 1–67.

■ Minor text edits.

June 2011

4.1

■ Added Table 1–60.

■ Updated Table 1–32, Table 1–33, Table 1–38, Table 1–41, and Table 1–61.

■ Updated the “Switching Characteristics” section introduction.

■ Minor text edits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSC44DRAH-S734 | CONN EDGECARD 88POS .100 R/A PCB |

| EP2AGX190EF29C4N | IC ARRIA II GX FPGA 190K 780FBGA |

| FMC22DRYN | CONN EDGECARD 44POS DIP .100 SLD |

| EP1S30F780I6 | IC STRATIX FPGA 30K LE 780-FBGA |

| EP2SGX60EF1152I4 | IC STRATIX II GX 60K 1152-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP2AGX190FF35C4 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C4N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C5 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C5N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C6 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。