- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4495 > EP4CE22E22C6N (Altera)IC CYCLONE IV FPGA 22K 144EQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EP4CE22E22C6N |

| 廠商: | Altera |

| 文件頁數(shù): | 35/42頁 |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV FPGA 22K 144EQFP |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 120 |

| 系列: | CYCLONE® IV E |

| LAB/CLB數(shù): | 1395 |

| 邏輯元件/單元數(shù): | 22320 |

| RAM 位總計(jì): | 608256 |

| 輸入/輸出數(shù): | 79 |

| 電源電壓: | 1.15 V ~ 1.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 144-LQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 144-EQFP(20x20) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

1–40

Chapter 1: Cyclone IV Device Datasheet

Glossary

December 2013

Altera Corporation

T

tC

High-speed receiver and transmitter input and output clock period.

Channel-to-

channel-skew

(TCCS)

High-speed I/O block: The timing difference between the fastest and slowest output edges,

including tCO variation and clock skew. The clock is included in the TCCS measurement.

tcin

Delay from the clock pad to the I/O input register.

tCO

Delay from the clock pad to the I/O output.

tcout

Delay from the clock pad to the I/O output register.

tDUTY

High-speed I/O block: Duty cycle on high-speed transmitter output clock.

tFALL

Signal high-to-low transition time (80–20%).

tH

Input register hold time.

Timing Unit

Interval (TUI)

High-speed I/O block: The timing budget allowed for skew, propagation delays, and data

sampling window. (TUI = 1/(Receiver Input Clock Frequency Multiplication Factor) = tC/w).

tINJITTER

Period jitter on the PLL clock input.

tOUTJITTER_DEDCLK

Period jitter on the dedicated clock output driven by a PLL.

tOUTJITTER_IO

Period jitter on the general purpose I/O driven by a PLL.

tpllcin

Delay from the PLL inclk pad to the I/O input register.

tpllcout

Delay from the PLL inclk pad to the I/O output register.

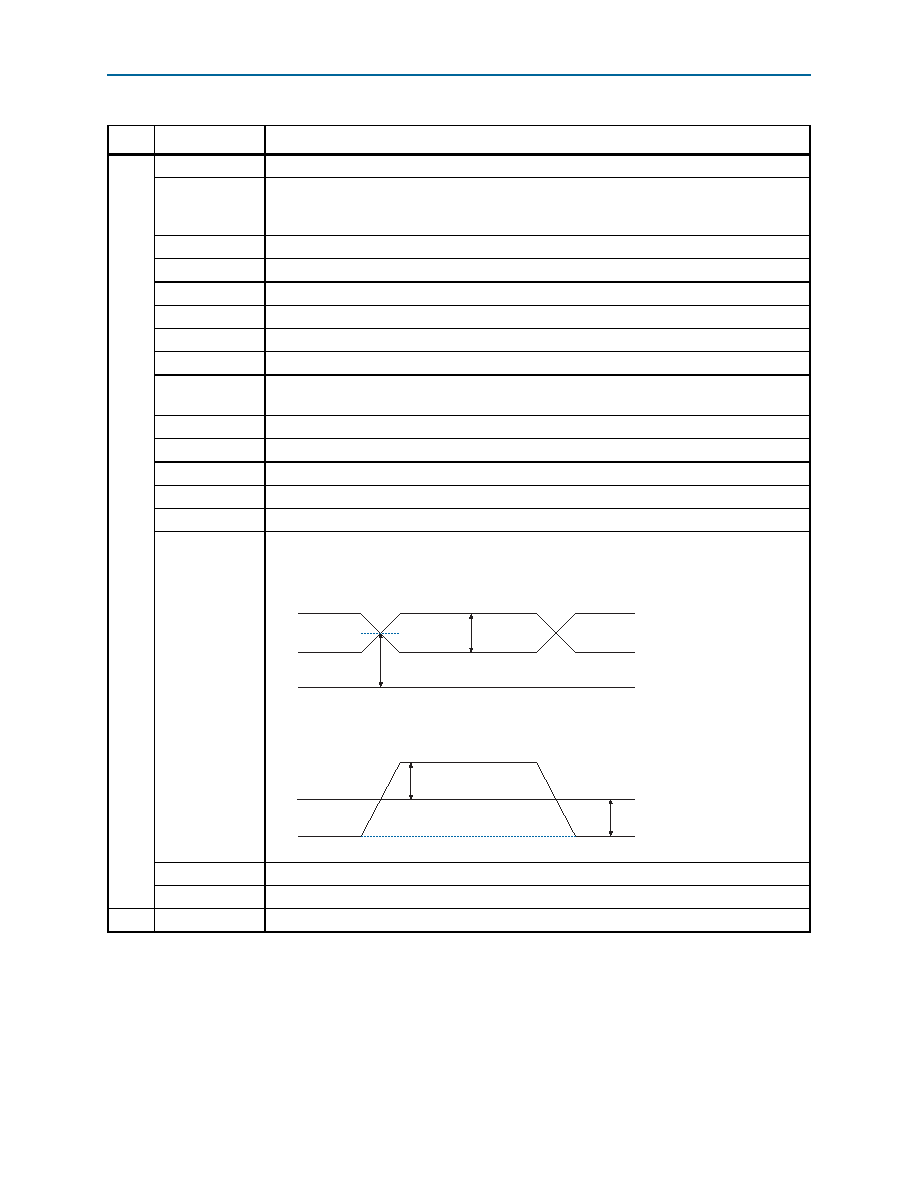

Transmitter

Output

Waveform

Transmitter output waveforms for the LVDS, mini-LVDS, PPDS and RSDS Differential I/O

Standards:

tRISE

Signal low-to-high transition time (20–80%).

tSU

Input register setup time.

U

——

Table 1–46. Glossary (Part 4 of 5)

Letter

Term

Definitions

Single-Ended Waveform

Differential Waveform (Mathematical Function of Positive & Negative Channel)

Positive Channel (p) = V

OH

Negative Channel (n) = V

OL

Ground

VOD

V

OD

V

OD

0 V

Vos

p

- n

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A40MX04-VQ80I | IC FPGA MX SGL CHIP 6K 80-VQFP |

| A40MX04-1VQ80 | IC FPGA MX SGL CHIP 6K 80-VQFP |

| EPF6016ATC144-1N | IC FLEX 6000 FPGA 16K 144-TQFP |

| EPF6016ATC144-1 | IC FLEX 6000 FPGA 16K 144-TQFP |

| AGM31DTBN-S189 | CONN EDGECARD 62POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CE22E22C7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV E 1395 LABs 79 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE22E22C7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV E 1395 LABs 79 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE22E22C8 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV E 1395 LABs 79 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE22E22C8L | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV E 1395 LABs 79 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE22E22C8LN | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV E 1395 LABs 79 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。