- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4491 > EP4CE30F29C8L (Altera)IC CYCLONE IV FPGA 30K 780FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4CE30F29C8L |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 28/42頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC CYCLONE IV FPGA 30K 780FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 36 |

| 系列: | CYCLONE® IV E |

| LAB/CLB數(shù): | 1803 |

| 邏輯元件/單元數(shù): | 28848 |

| RAM 位總計(jì): | 608256 |

| 輸入/輸出數(shù): | 532 |

| 電源電壓: | 0.97 V ~ 1.03 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 780-BBGA |

| 供應(yīng)商設(shè)備封裝: | 780-FBGA(29x29) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

1–34

Chapter 1: Cyclone IV Device Datasheet

Switching Characteristics

December 2013

Altera Corporation

IOE Programmable Delay

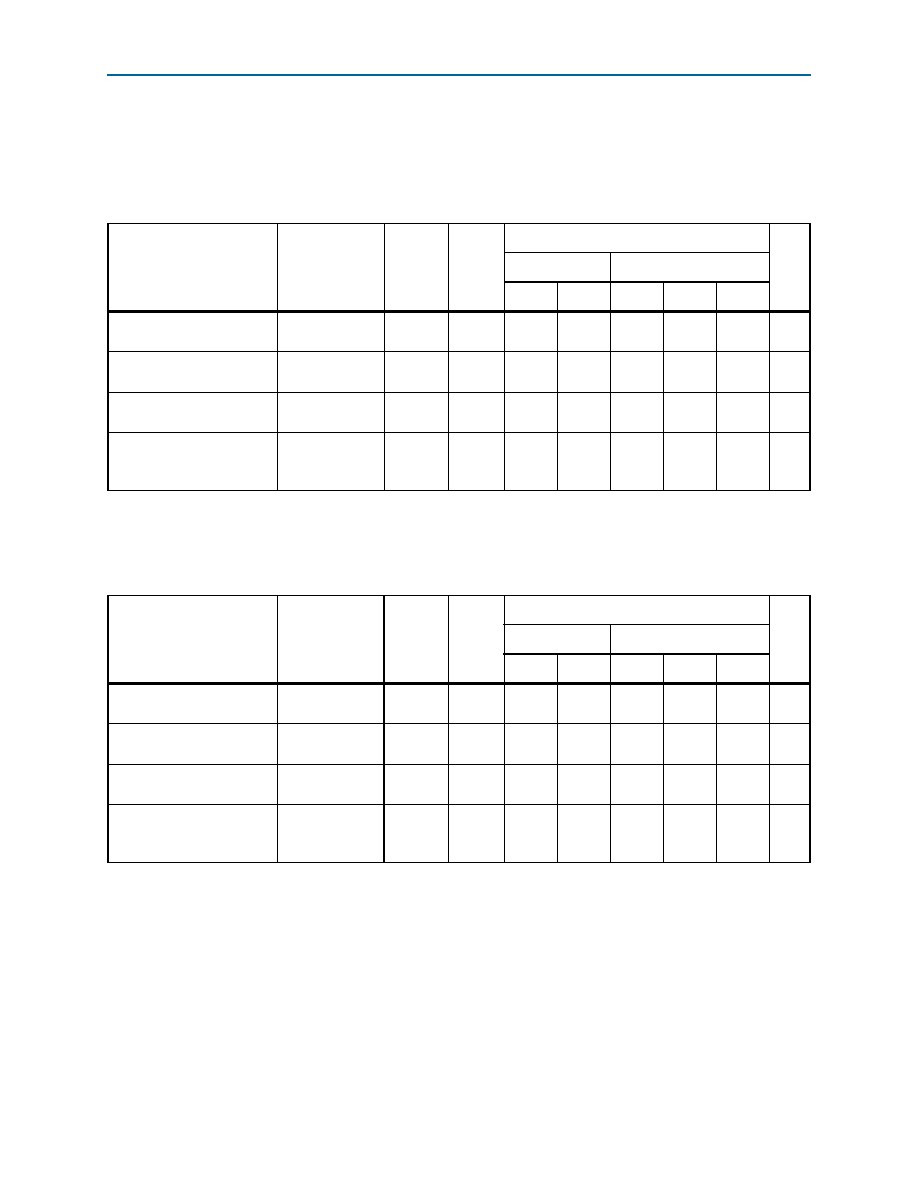

Table 1–40 and Table 1–41 list the IOE programmable delay for Cyclone IV E 1.0 V

core voltage devices.

Table 1–40. IOE Programmable Delay on Column Pins for Cyclone IV E 1.0 V Core Voltage Devices (1), (2)

Parameter

Paths Affected

Number

of

Setting

Min

Offset

Max Offset

Unit

Fast Corner

Slow Corner

C8L

I8L

C8L

C9L

I8L

Input delay from pin to

internal cells

Pad to I/O

dataout to core

7

0

2.054

1.924

3.387

4.017

3.411

ns

Input delay from pin to

input register

Pad to I/O input

register

8

0

2.010

1.875

3.341

4.252

3.367

ns

Delay from output register

to output pin

I/O output

register to pad

2

0

0.641

0.631

1.111

1.377

1.124

ns

Input delay from

dual-purpose clock pin to

fan-out destinations

Pad to global

clock network

12

0

0.971

0.931

1.684

2.298

1.684

ns

Notes to Table 1–40:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting 0 as available in the Quartus II software.

Table 1–41. IOE Programmable Delay on Row Pins for Cyclone IV E 1.0 V Core Voltage Devices (1), (2)

Parameter

Paths Affected

Number

of

Setting

Min

Offset

Max Offset

Unit

Fast Corner

Slow Corner

C8L

I8L

C8L

C9L

I8L

Input delay from pin to

internal cells

Pad to I/O

dataout to core

7

0

2.057

1.921

3.389

4.146

3.412

ns

Input delay from pin to

input register

Pad to I/O input

register

8

0

2.059

1.919

3.420

4.374

3.441

ns

Delay from output register

to output pin

I/O output

register to pad

2

0

0.670

0.623

1.160

1.420

1.168

ns

Input delay from

dual-purpose clock pin to

fan-out destinations

Pad to global

clock network

12

0

0.960

0.919

1.656

2.258

1.656

ns

Notes to Table 1–41:

(1) The incremental values for the settings are generally linear. For the exact values for each setting, use the latest version of the Quartus II software.

(2) The minimum and maximum offset timing numbers are in reference to setting 0 as available in the Quartus II software.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ABM43DTAD-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| RSC49DRYS-S93 | CONN EDGECARD 98POS DIP .100 SLD |

| RMC49DRYS-S93 | CONN EDGECARD 98POS DIP .100 SLD |

| IDT71V416S15YG8 | IC SRAM 4MBIT 15NS 44SOJ |

| W948D6FBHX5E | IC LPDDR SDRAM 256MBIT 60VFBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CE30F29C8LN | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV E 1803 LABs 532 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE30F29C8N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV E 1803 LABs 532 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE30F29C9L | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV E 1803 LABs 532 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE30F29C9LN | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV E 1803 LABs 532 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE30F29I7 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV E 1803 LABs 532 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。