- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19361 > EP4CE6F17I8LN (Altera)IC CYCLONE IV E FPGA 6K 256FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4CE6F17I8LN |

| 廠(chǎng)商: | Altera |

| 文件頁(yè)數(shù): | 26/42頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV E FPGA 6K 256FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Designing an IP Surveillance Camera Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | CYCLONE® IV E |

| LAB/CLB數(shù): | 392 |

| 邏輯元件/單元數(shù): | 6272 |

| RAM 位總計(jì): | 276480 |

| 輸入/輸出數(shù): | 179 |

| 電源電壓: | 0.97 V ~ 1.03 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 256-BGA |

| 供應(yīng)商設(shè)備封裝: | 256-FBGA(17x17) |

| 產(chǎn)品目錄頁(yè)面: | 602 (CN2011-ZH PDF) |

| 其它名稱(chēng): | 544-2651 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

1–32

Chapter 1: Cyclone IV Device Datasheet

Switching Characteristics

December 2013

Altera Corporation

External Memory Interface Specifications

The external memory interfaces for Cyclone IV devices are auto-calibrating and easy

to implement.

tDUTY

—

455545554555455545

55

%

TCCS

—

200

—

200

—

200

—

200

—

200

ps

Output jitter

(peak to peak)

—

500

—

500

—

550

—

600

—

700

ps

tLOCK (2)

—

1—

1

ms

Notes to Table 1–35:

(1) Cyclone IV E—emulated LVDS transmitter is supported at the output pin of all I/O Banks.

Cyclone IV GX—emulated LVDS transmitter is supported at the output pin of I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2) tLOCK is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support

C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

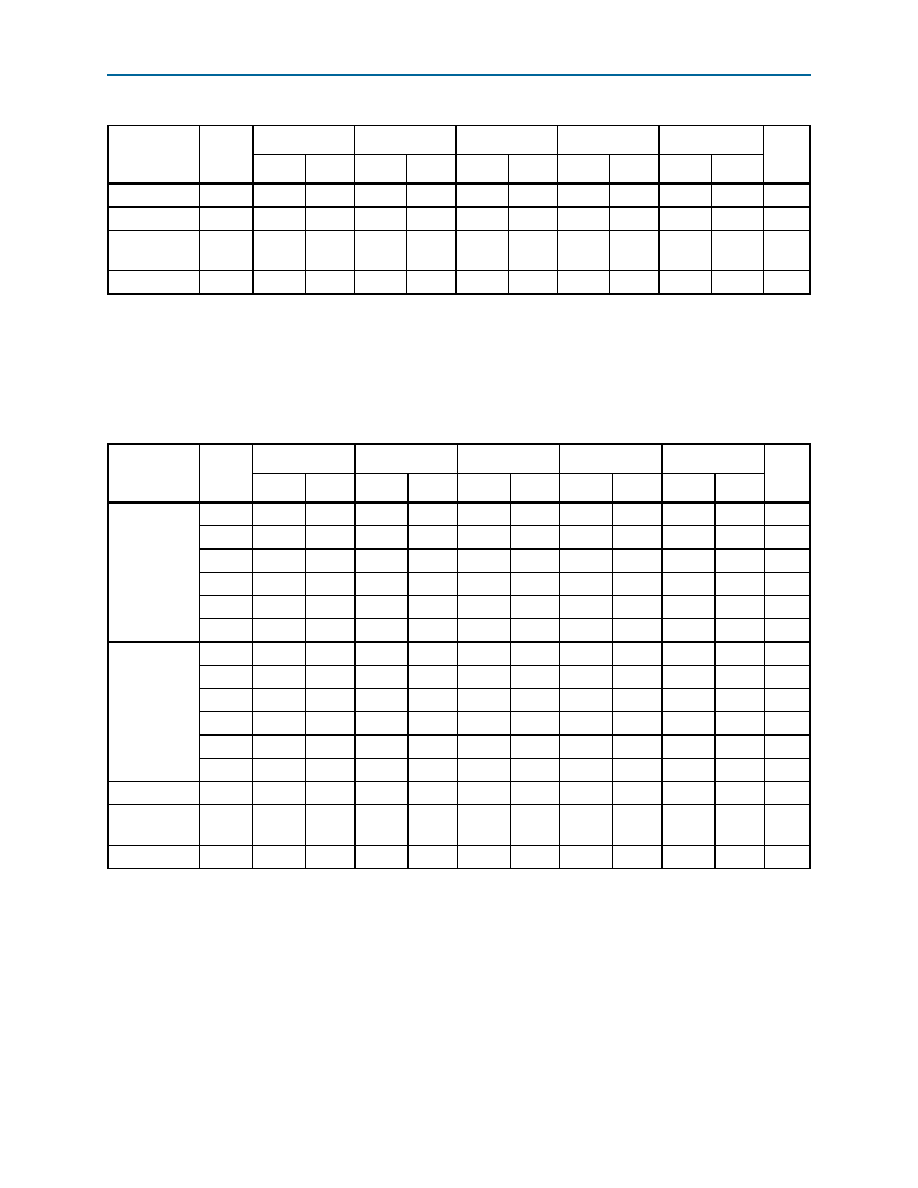

Table 1–35. Emulated LVDS Transmitter Timing Specifications for Cyclone IV Devices (1), (3) (Part 2 of 2)

Symbol

Modes

C6

C7, I7

C8, A7

C8L, I8L

C9L

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Table 1–36. LVDS Receiver Timing Specifications for Cyclone IV Devices (1), (3)

Symbol

Modes

C6

C7, I7

C8, A7

C8L, I8L

C9L

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

fHSCLK (input

clock

frequency)

×10

10

437.5

10

370

10

320

10

320

10

250

MHz

×8

10

437.5

10

370

10

320

10

320

10

250

MHz

×7

10

437.5

10

370

10

320

10

320

10

250

MHz

×4

10

437.5

10

370

10

320

10

320

10

250

MHz

×2

10

437.5

10

370

10

320

10

320

10

250

MHz

×1

10

437.5

10

402.5

10

402.5

10

362

10

265

MHz

HSIODR

×10

100

875

100

740

100

640

100

640

100

500

Mbps

×8

80

875

80

740

80

640

80

640

80

500

Mbps

×7

70

875

70

740

70

640

70

640

70

500

Mbps

×4

40

875

40

740

40

640

40

640

40

500

Mbps

×2

20

875

20

740

20

640

20

640

20

500

Mbps

×1

10

437.5

10

402.5

10

402.5

10

362

10

265

Mbps

SW

—

400

—

400

—

400

—

550

—

640

ps

Input jitter

tolerance

—

500

—

500

—

550

—

600

—

700

ps

tLOCK (2)

—

—1—1—1—1—

1

ms

Notes to Table 1–36:

(1) Cyclone IV E—LVDS receiver is supported at all I/O Banks.

Cyclone IV GX—LVDS receiver is supported at I/O Banks 3, 4, 5, 6, 7, 8, and 9.

(2) tLOCK is the time required for the PLL to lock from the end-of-device configuration.

(3) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support

C6, C7, C8, I7, and A7 speed grades. Cyclone IV GX devices only support C6, C7, C8, and I7 speed grades.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T525D227M004ATE025 | CAP TANT 220UF 4V 20% 2917 |

| TPSD686M016R0150 | CAP TANT 68UF 16V 20% 2917 |

| VI-B6Z-CW-F1 | CONVERTER MOD DC/DC 2V 40W |

| MAX6649YMUA+ | IC SENSOR REMOTE SMBUS 8UMAX |

| LT3517EUF#PBF | IC LED DRIVER AUTOMOTIVE 16-QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CE6F23C8N | 制造商:ALTERA 制造商全稱(chēng):Altera Corporation 功能描述:Cyclone IV FPGA Device Faily Overview |

| EP4CE6F23I7N | 制造商:ALTERA 制造商全稱(chēng):Altera Corporation 功能描述:Cyclone IV Device Datasheet |

| EP4CE6U14I7N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Cyclone IV E 392 LABs 179 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75 | 制造商:ALTERA 制造商全稱(chēng):Altera Corporation 功能描述:Cyclone IV Device Datasheet |

| EP4CE75F17C8 | 制造商:ALTERA 制造商全稱(chēng):Altera Corporation 功能描述:Cyclone IV Device Datasheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。