- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4404 > EP4CGX110CF23C8N (Altera)IC CYCLONE IV FPGA 110K 484FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4CGX110CF23C8N |

| 廠商: | Altera |

| 文件頁數(shù): | 33/42頁 |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV FPGA 110K 484FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | CYCLONE® IV GX |

| LAB/CLB數(shù): | 6839 |

| 邏輯元件/單元數(shù): | 109424 |

| RAM 位總計(jì): | 5621760 |

| 輸入/輸出數(shù): | 270 |

| 電源電壓: | 1.16 V ~ 1.24 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 484-BGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA(23x23) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Chapter 1: Cyclone IV Device Datasheet

1–39

Glossary

December 2013

Altera Corporation

R

RL

Receiver differential input discrete resistor (external to Cyclone IV devices).

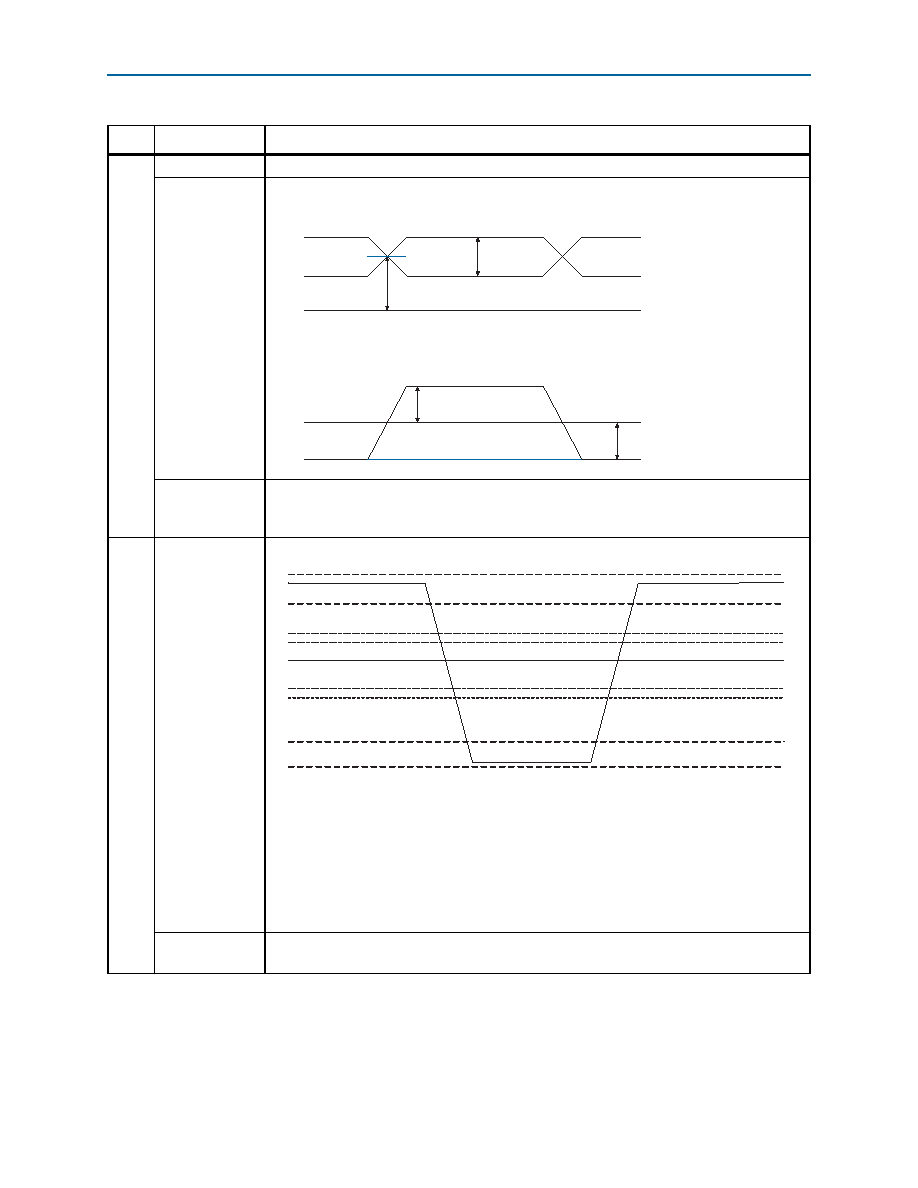

Receiver Input

Waveform

Receiver input waveform for LVDS and LVPECL differential standards:

Receiver input

skew margin

(RSKM)

High-speed I/O block: The total margin left after accounting for the sampling window and TCCS.

RSKM = (TUI – SW – TCCS) / 2.

S

Single-ended

voltage-

referenced I/O

Standard

The JEDEC standard for SSTl and HSTL I/O standards defines both the AC and DC input signal

values. The AC values indicate the voltage levels at which the receiver must meet its timing

specifications. The DC values indicate the voltage levels at which the final logic state of the

receiver is unambiguously defined. After the receiver input crosses the AC value, the receiver

changes to the new logic state. The new logic state is then maintained as long as the input stays

beyond the DC threshold. This approach is intended to provide predictable receiver timing in the

presence of input waveform ringing.

SW (Sampling

Window)

High-speed I/O block: The period of time during which the data must be valid to capture it

correctly. The setup and hold times determine the ideal strobe position in the sampling window.

Table 1–46. Glossary (Part 3 of 5)

Letter

Term

Definitions

Single-Ended Waveform

Differential Waveform (Mathematical Function of Positive & Negative Channel)

Positive Channel (p) = V

IH

Negative Channel (n) = V

IL

Ground

V

ID

V

ID

0 V

V

CM

p

- n

V

ID

VIH(AC)

VIH(DC)

VREF

VIL(DC)

VIL(AC)

VOH

VOL

VCCIO

VSS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A54SX32-BG313 | IC FPGA SX 48K GATES 313-BGA |

| EP4CE75F29C9L | IC CYCLONE IV FPGA 75K 780FBGA |

| EP4CE75F29C8 | IC CYCLONE IV FPGA 75K 780FBGA |

| M1AGL1000V2-FGG256I | IC FPGA 1KB FLASH 1M 256-FBGA |

| AGL1000V2-FG256I | IC FPGA 1KB FLASH 1M 256FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CGX110CF23I7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 270 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110CF23I7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 270 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF27C7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 393 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF27C7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 393 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF27C8 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 393 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。