- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19328 > EP4CGX110DF31C7N (Altera)IC CYCLONE IV FPGA 110K 896FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EP4CGX110DF31C7N |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 40/42頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV FPGA 110K 896FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Designing an IP Surveillance Camera Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產(chǎn)品: | Cyclone? IV FPGAs |

| 標(biāo)準(zhǔn)包裝: | 27 |

| 系列: | CYCLONE® IV GX |

| LAB/CLB數(shù): | 6839 |

| 邏輯元件/單元數(shù): | 109424 |

| RAM 位總計(jì): | 5621760 |

| 輸入/輸出數(shù): | 475 |

| 電源電壓: | 1.16 V ~ 1.24 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 896-BBGA |

| 供應(yīng)商設(shè)備封裝: | 896-FBGA(31x31) |

| 其它名稱: | 544-2673 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)

Chapter 1: Cyclone IV Device Datasheet

1–7

Operating Conditions

December 2013

Altera Corporation

DC Characteristics

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT)

tolerance, and bus hold specifications for Cyclone IV devices.

Supply Current

The device supply current requirement is the minimum current drawn from the

power supply pins that can be used as a reference for power size planning. Use the

Excel-based early power estimator (EPE) to get the supply current estimates for your

design because these currents vary greatly with the resources used. Table 1–6 lists the

I/O pin leakage current for Cyclone IV devices.

Bus Hold

The bus hold retains the last valid logic state after the source driving it either enters

the high impedance state or is removed. Each I/O pin has an option to enable bus

hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Symbol

Parameter

Conditions

Device

Min

Typ

Max

Unit

II

Input pin leakage current

VI = 0 V to VCCIOMAX

—

–10

—

10

A

IOZ

Tristated I/O pin leakage

current

VO = 0 V to VCCIOMAX

—

–10

—

10

A

Notes to Table 1–6:

(1) This value is specified for normal device operation. The value varies during device power

-up. This applies for all VCCIO settings (3.3, 3.0, 2.5,

1.8, 1.5, and 1.2 V).

(2) The 10

A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

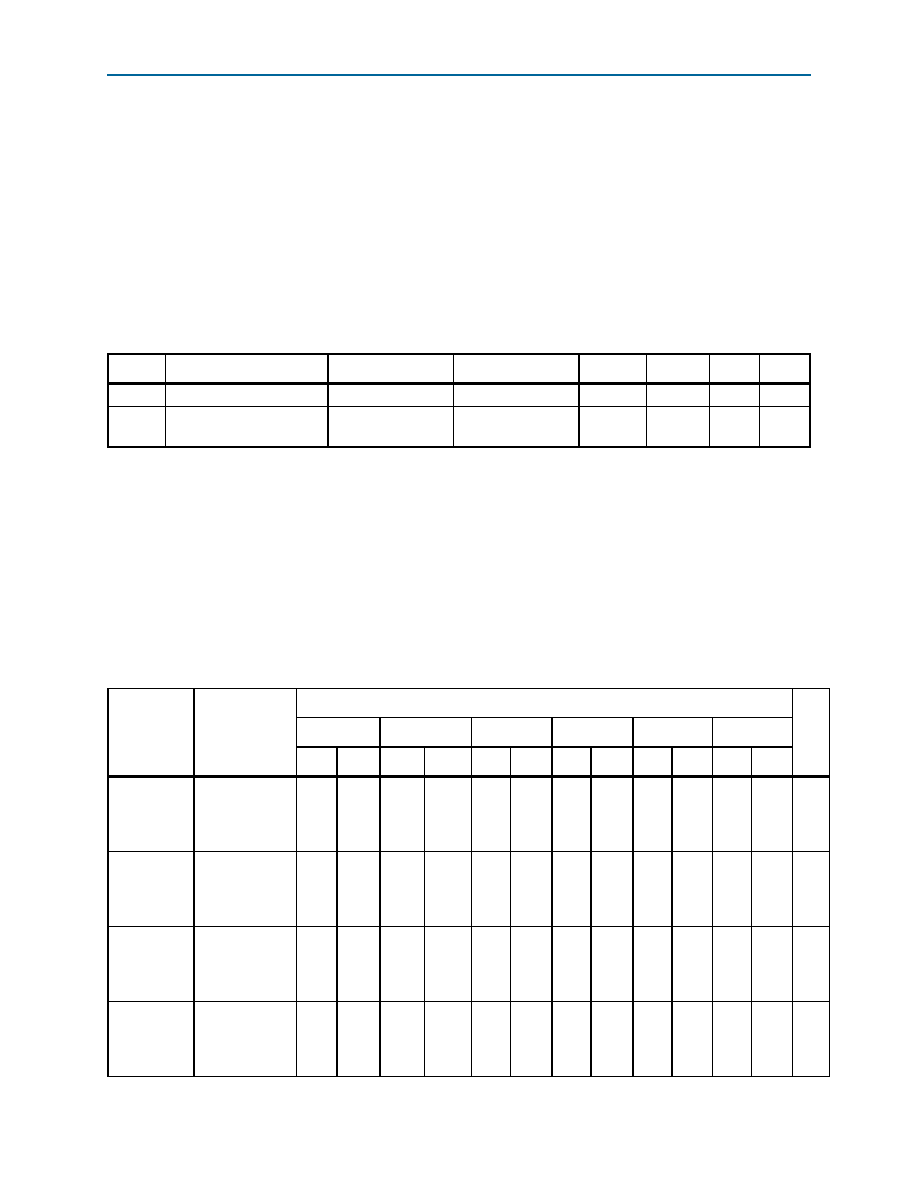

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2) (1)

Parameter

Condition

VCCIO (V)

Unit

1.2

1.5

1.8

2.5

3.0

3.3

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Bus hold

low,

sustaining

current

VIN > VIL

(maximum)

8

—

12

—

30—50—70

—

70

—

A

Bus hold

high,

sustaining

current

VIN < VIL

(minimum)

–8

—

–12

—

–30

—

–50

—

–70

—

–70

—

A

Bus hold

low,

overdrive

current

0 V < VIN < VCCIO

—

125

—

175

—

200

—

300

—

500

—

500

A

Bus hold

high,

overdrive

current

0 V < VIN < VCCIO

—

–125

—

–175

—

–200

—

–300

—

–500

—

–500

A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EBC05DRAH | CONN EDGECARD 10POS R/A .100 SLD |

| VE-B4W-EU-S | CONVERTER MOD DC/DC 5.5V 200W |

| REC3-243.3SRWZ/H2/C | CONV DC/DC 3W 9-36VIN 3.3VOUT |

| VI-B5M-CV-F4 | CONVERTER MOD DC/DC 10V 150W |

| RBM11DRUI | CONN EDGECARD 22POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4CGX110DF31C8 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 475 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF31C8N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 475 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF31I7 | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 475 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110DF31I7N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 FPGA - Cyclone IV GX 6839 LABs 475 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CGX110F17C8 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Cyclone IV Device Datasheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。